LVDS的GCLK接收方案

时间:2024-08-12 | 栏目:可编程逻辑 | 点击:次

在易灵思的器件上接收LVDS一般采用PLL接收,通过PLL产生两个时钟,一个是fast_clk,一个是slow_clk,分别用于处理串行数据和并行数据。

但是如果LVDS的速率比较低时,另外想通过去掉PLL来节省功耗时,也可以直接用lvds_rx_clk直接走GCLK的方式来处理。下面我们来说明一下:

硬件环境如下:

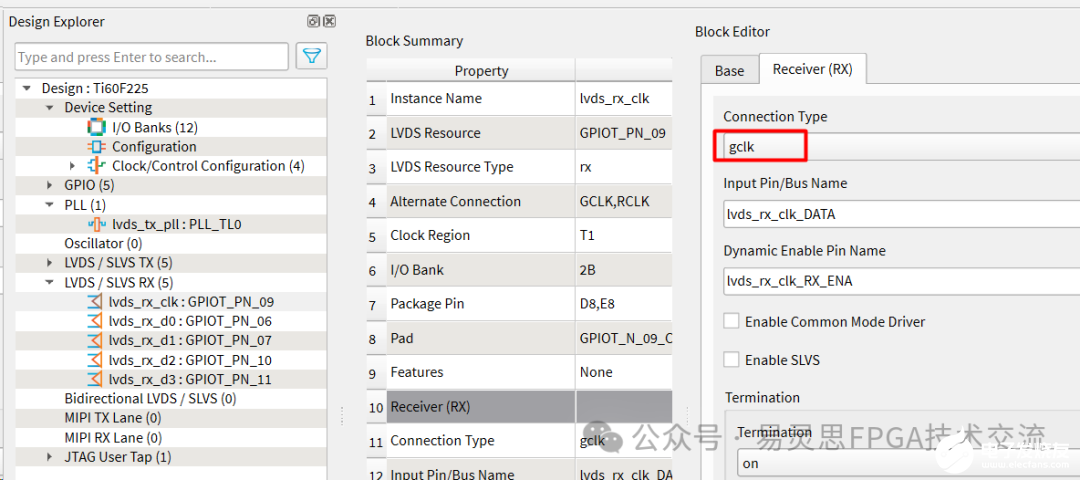

打开interface在里面设置LVDS

LVDS的时钟接收Connection Type选择gclk。

对于数据设置串化因子为2,并输入Parallel Clock名字为上面定义的时钟。

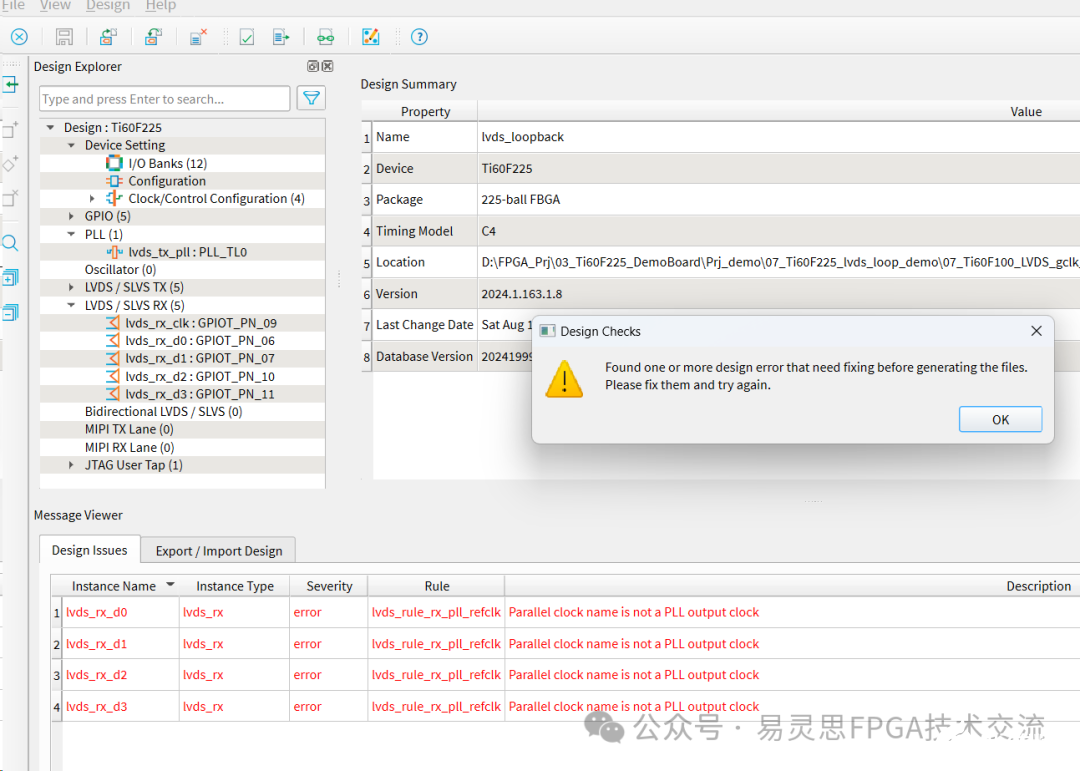

在一切都设置好之后需要生成约束。但是会报以下错误。

但是解决办法是有的。在工程目录下新建pt_rule.ini文件,输入lvds_rule_rx_pll_refclk,再次生成结束可以正常。

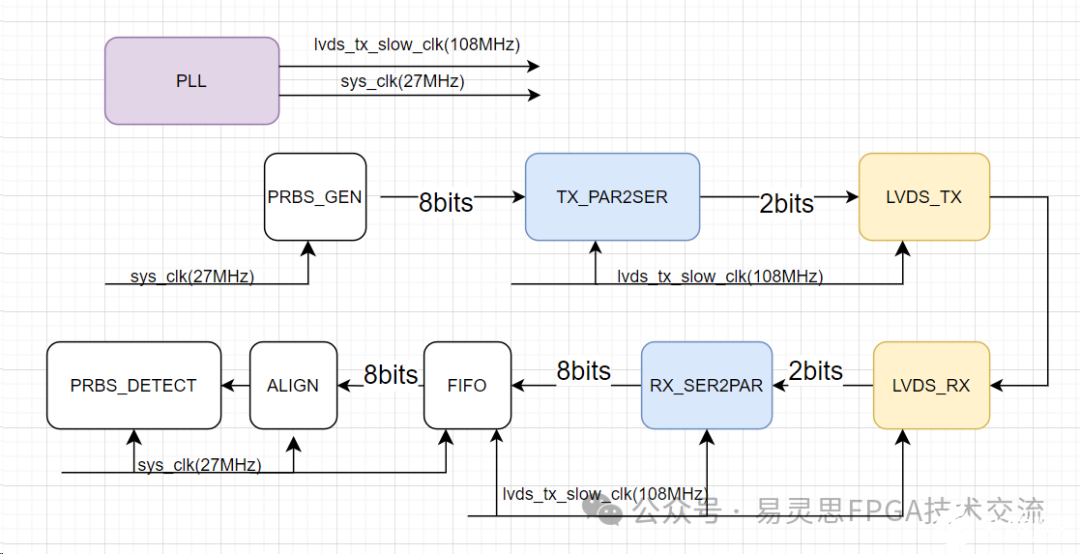

程序框图如下: