FPGA优质开源模块-SRIO IP核的使用

时间:2023-12-12 | 栏目:可编程逻辑 | 点击:次

本文介绍一个FPGA常用模块:SRIO(SerialRapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

由于Vivado中RapidIO IP核需要付费才能使用,因此本文提供完整工程源码。文章末尾有该工程源码获取方式,有需要的小伙伴可以收藏、分享一下。

01

软硬件平台

软件平台:Vivado 2017.4;

硬件平台:XC7K410T...;

02

IP核参数配置

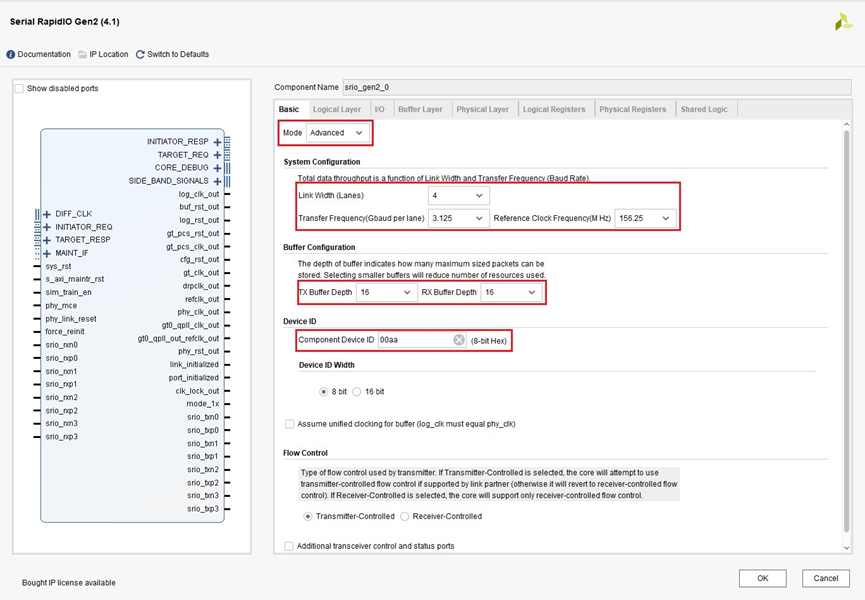

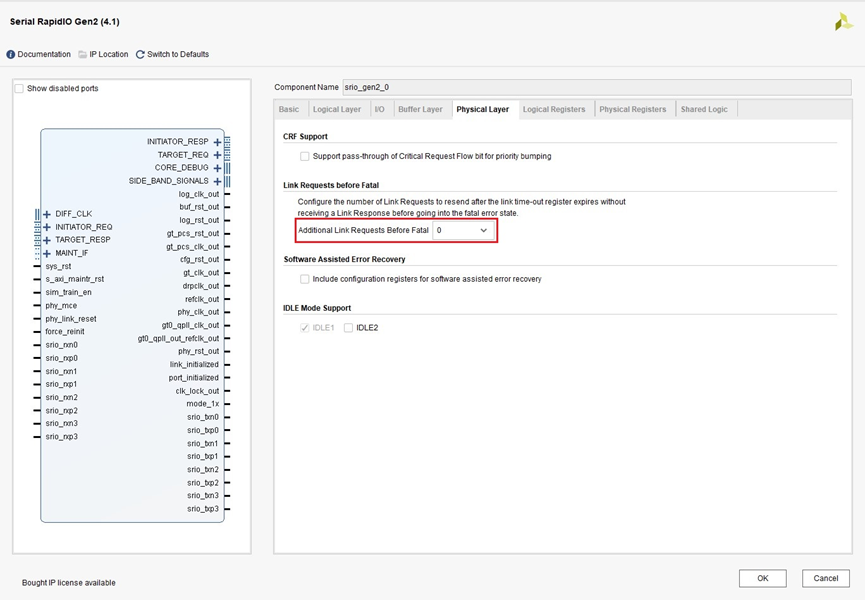

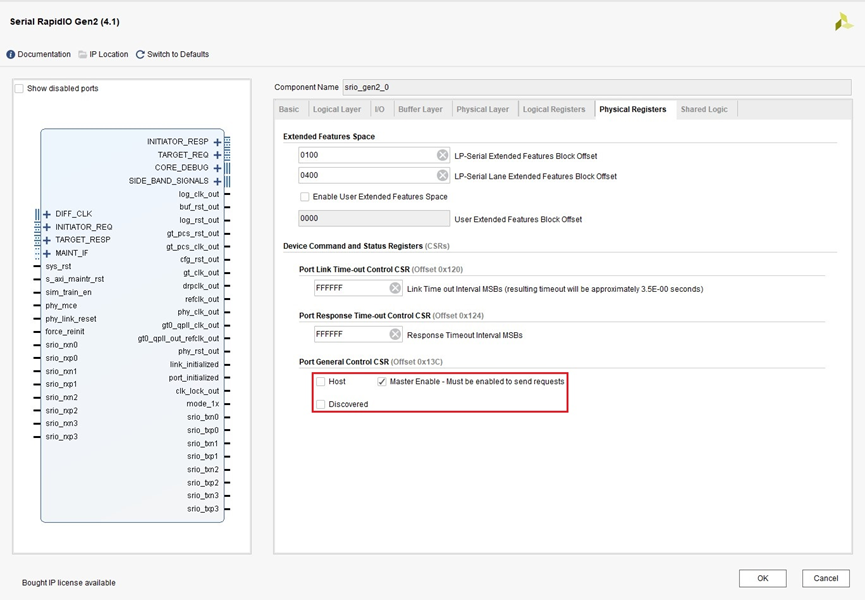

本工程SRIO IP核参数配置如下图所示,仅供参考:

03

工程源码结构

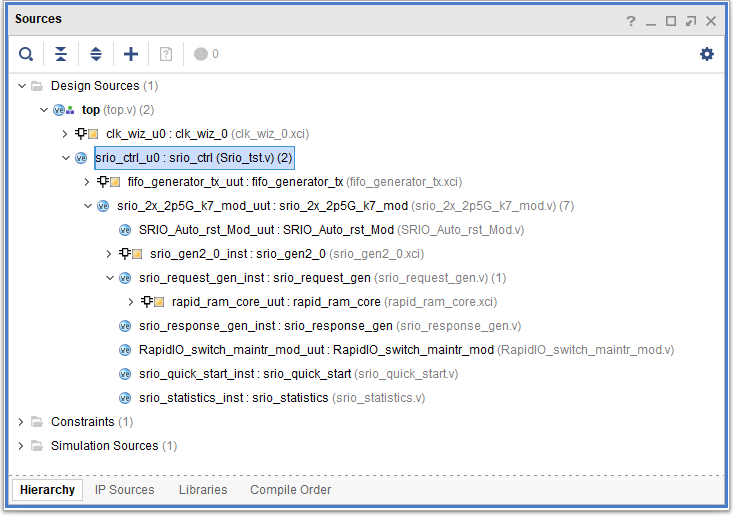

下图是SRIO工程源码结构:

其中,

SRIO_Auto_rst_Mod:SRIO自动复位模块;

srio_request_gen:SRIO请求事务生成模块;

srio_response_gen:SRIO响应事务生成模块;

RapidIO_switch_maintr_mod & srio_quick_start:SRIO维护事务生成模块。

04

实现功能

该FPGA SRIO模块采用NWRITE类型事务往DSP目的地址传输数据,每包数据大小为256字节。数据写入完毕后,通过DOORBELL事务给DSP发送数据接收中断。另外FPGA端通过RapidIO IP核m_axis_treq接口接收来自DSP的数据。

审核编辑:刘清