Xilinx FPGA芯片内部时钟和复位信号使用方法

时间:2023-10-27 | 栏目:可编程逻辑 | 点击:次

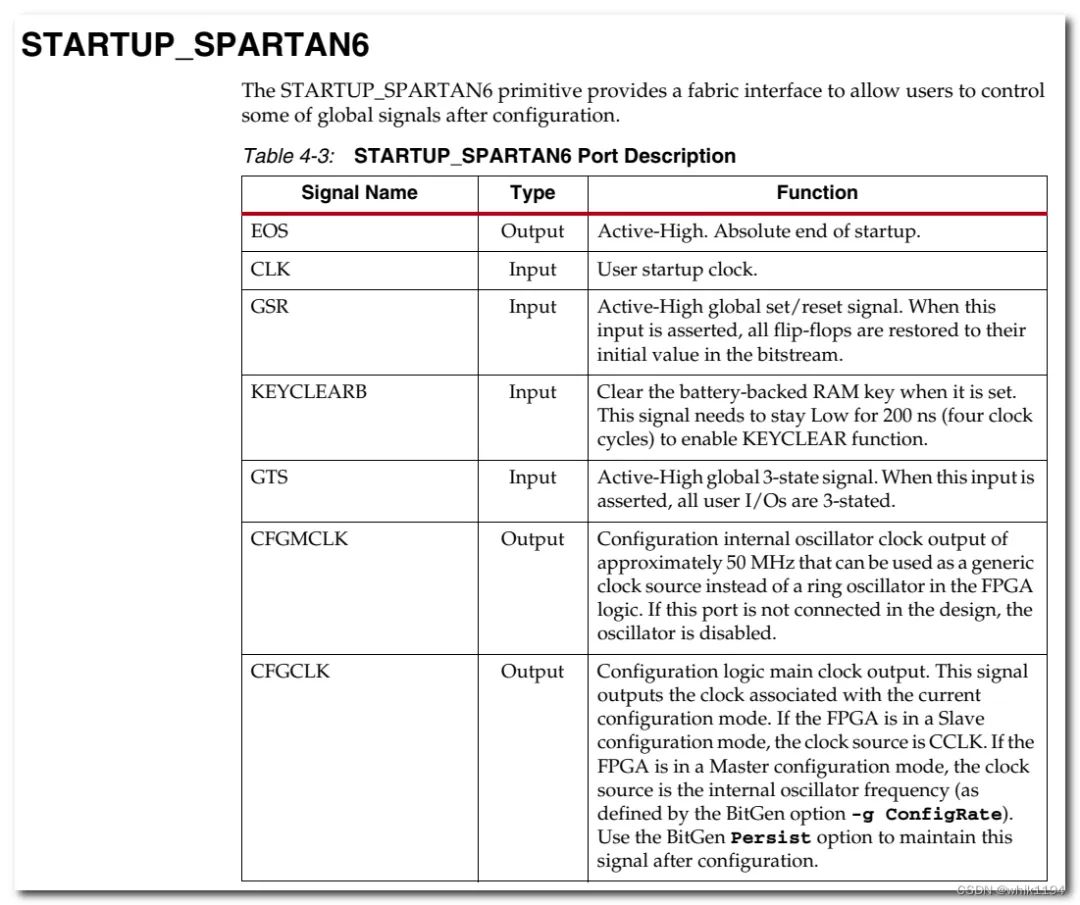

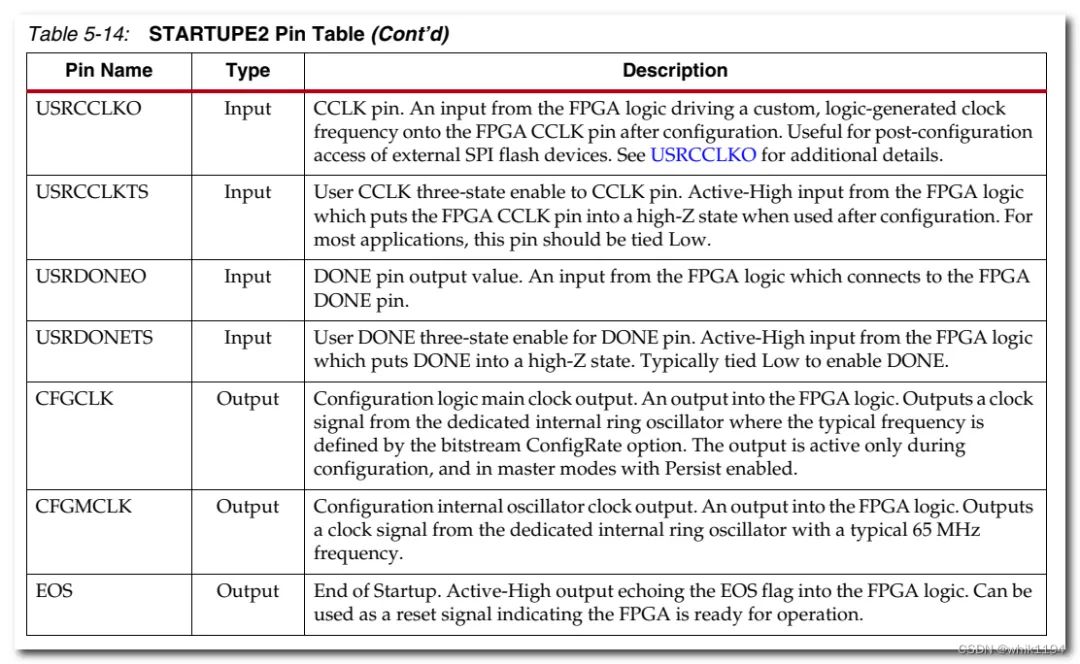

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

Spartan-6系列

wireclk_50m; wirerst_n; STARTUP_SPARTAN6STARTUP_SPARTAN6_inst( .CFGMCLK(clk_50m),//1-bitoutput:Configurationinternaloscillatorclockoutput. .EOS(rst_n),//1-bitoutput:ActivehighoutputsignalindicatestheEndOfConfiguration. );

Artix-7(7系列)

wireclk_65m; wirerst_n; STARTUPE2STARTUPE2_ut0( .CFGMCLK(clk_65m),//1-bitoutput:Configurationinternaloscillatorclockoutput65MHz. .EOS(rst_n)//1-bitoutput:ActivehighoutputsignalindicatingtheEndOfStartup. );

分别可以参考文档:

UG380:Spartan-6 FPGA Configuration

UG470:7 Series FPGAs Configuration

审核编辑:刘清