以计数器为32位为例:FPGA中计数器设计探索

时间:2018-03-24 | 栏目:模拟技术 | 点击:次

我知道,我对与电子有关的所有事情都很着迷,但不论从哪个角度看,今天的现场可编程门阵列(FPGA),都显得“鹤立鸡群”,真是非常棒的器件。如果在这个智能时代,在这个领域,想拥有一技之长的你还没有关注FPGA,那么世界将抛弃你,时代将抛弃你。

FPGA中计数器设计探索,以计数器为32位为例:

第一种方式,直接定义32位计数器。

reg [31:0]count;

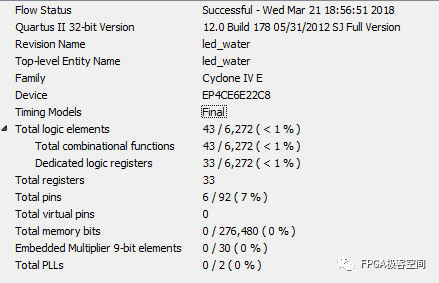

quartus ii 下的编译,资源消耗情况。

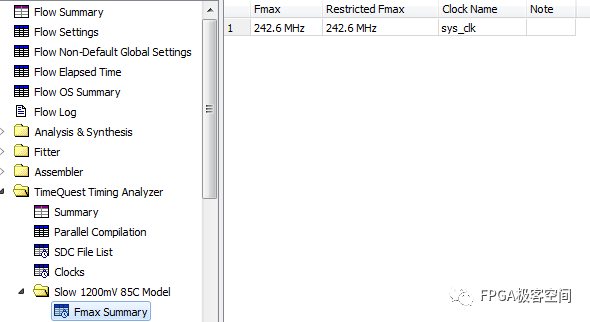

85C模型下的时钟频率。

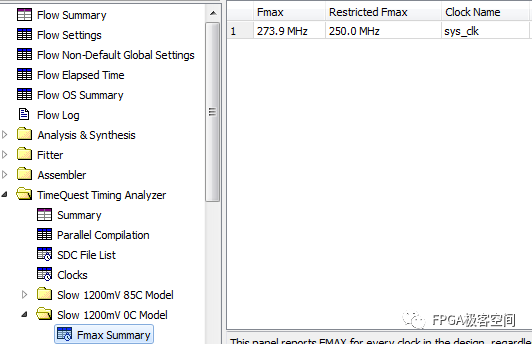

0C模型下的时钟频率。

chip planner下资源分布情况。

第二种方式,定义2个16位计数器。

reg [15:0]count1,count2;

quartus ii 下的编译,资源消耗情况。

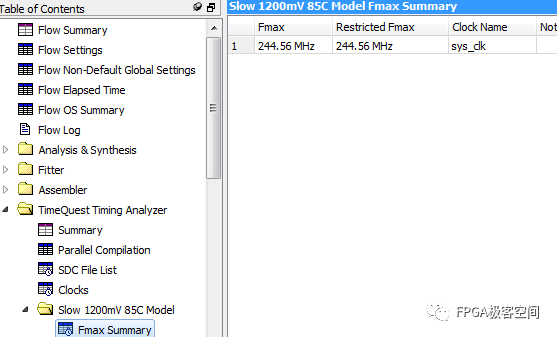

85C模型下的时钟频率。

0C模型下的时钟频率。

chip planner下资源分布情况

从上述两种情况来看,结合C4内部LAB的结构,两种方式消耗资源一样多,两种模型下的时钟频率比较接近。

值得注意的是,以上测试是在资源足够频率不高的条件下测试的。根据经验,当资源使用较多,时钟频频较高时,建议使用方式二。