时间:2025-02-24 10:37

人气:

作者:admin

案例72:PCB中铺“地”和“电源”要避免耦合

【现象描述】

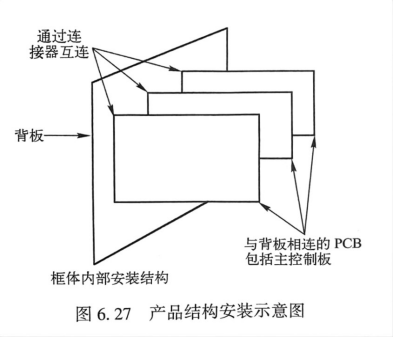

某产品采用框体背板结构,其他PCB插在背板上通过背板进行互连,正视面的底板安装背板PCB,其他PCB与背板垂直连接,产品结构安装示意图如图6.27所示。 框体采用-48 V直流供电。-48 V电源信号通过背板传送到插在框体并与背板相连的各个PCB中。其中,主控制板是框体系统的总控制系统。

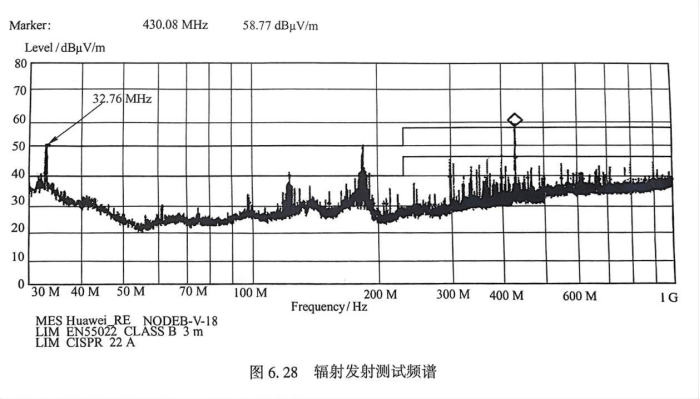

测试辐射发射时,发现在频点32.76 MHz处的辐射较高,准峰值为53.8dBμV/m,超过CLASS A限值近4dB,如图6.28所示。

在定位过程中发现,主控制板不插在槽位时就会消失,只要主控制板一插上,无论其他PCB如何配置,该点的辐射均存在。在定位过程中还发现,如在电源线上串磁环,则该点的辐射也将消失,这说明该点是通过电源线进行辐射的,而该频点源头来自于主控板,耦合途径可能在主控制板上,也有可能在背板上。

【原因分析】

为了确定辐射源的耦合途径,首先对框体的背板和主控制板的PCB进行详细的检查。通过对背板及主控制板的PCB布线检查,发现干扰信号耦合到电源线的途径和原因有以下几种可能:

(1)背板上主控制板槽位的时钟布线离框体供电电源-48 V的地较近,同时与背板DGND的隔离距离为50mil,可能会耦合到电源线。

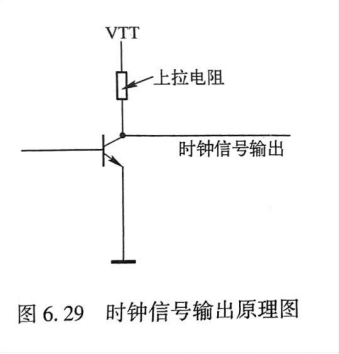

(2)时钟线布线是采用两端匹配的方式,通过上拉电阻匹配到VTT电源层。时钟信号输出原理图如图6.29所示。

如果VTT滤波电容选择的不合理,则可能会将干扰传入VTT层,而VTT层与-48 V的电源层在主控制板上有较大面积的重合,-48V电源层很有可能被耦合到干扰。

经过以上的初步分析可按以下步骤定位测试:

步骤一

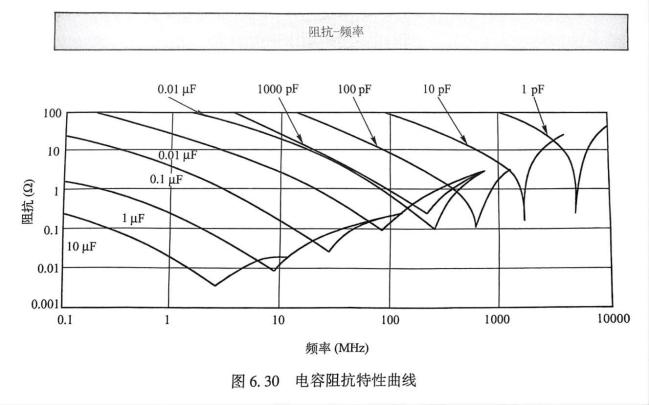

优化框体背板时钟匹配电阻的滤波电容,改为0.1μF和0.022μF。

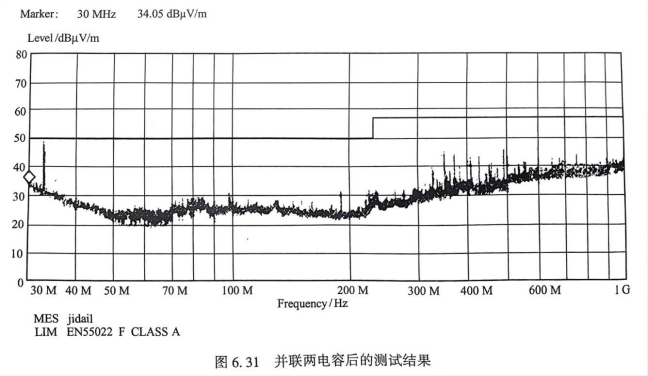

由如图6.30所示的电容阻抗特性曲线可知,两电容并联后的滤波范围在几十兆赫兹之间。修改完后,再进行测试,并联两电容后的测试结果如图6.31所示。

图6.31中的测试结果与以前的测试结果相比有改善,说明干扰与VTT电源层有关,但是耦合发生在背板还是主控制板,需要进行进一步的定位。

步骤二

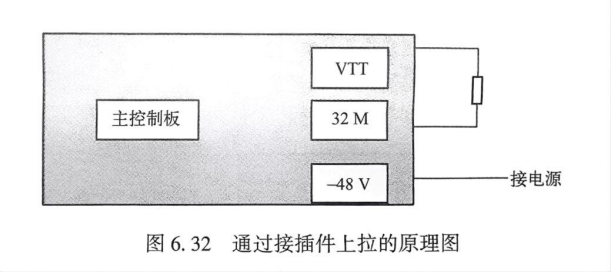

利用专门加工的接插件将主控制板输出的32.768 MHz时钟上拉到VTT制板,然后启动主控制板,通过接插件上拉的原理图如图6.32所示。

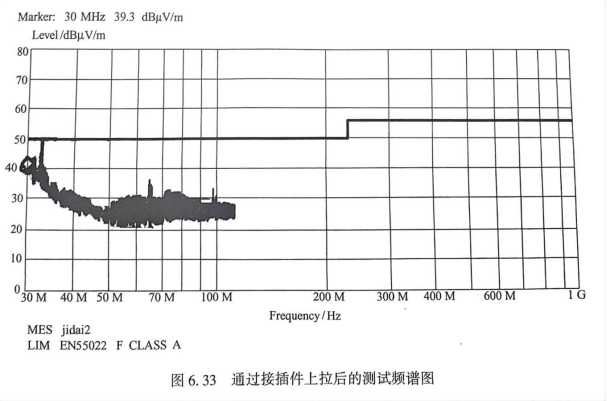

通过接插件上拉后冉进行测试,结果如图6.33所示。

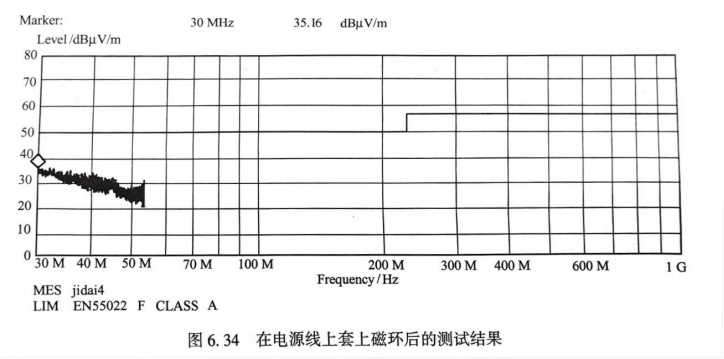

再在电源线上套上磁环后进行测试,得到如图6.34所示的结果。

到此为止,基本上可以说明问题出在主控制板上,而不是背板上,是主控板内部存在耦合。需要进一步定位的是,耦合是由时钟线直接引起的还是由VTT电源层引起的。

步骤三

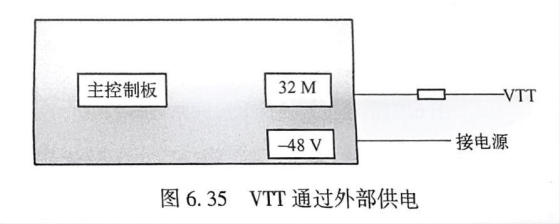

对主控制板进行处理,关断主控板的VTT电源,VTT通过外部线性电源供电,然后连接,如图6.35所示。

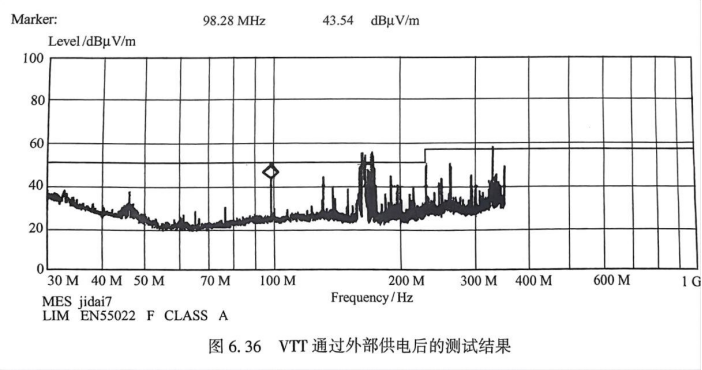

启动主控制板后再进行辐射测试,得到如图6.36所示的结果。

32.768 MHz时钟辐射基本消失,说明并不是由时钟线直接耦合到-48V电源层导致的辐射超标,而是由时钟信号的VTT电源层受到时钟信号的影响后对-48 V电源层耦合造成的。

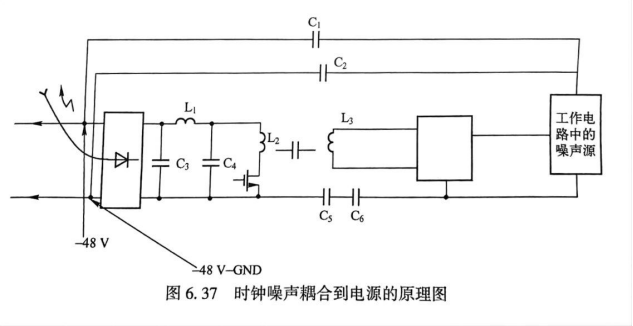

试验证明,32.768 MHz时钟的辐射是主控制板内通过VTT耦合到-48V电源层后,再对主控制板进行审查,发现VTT电源层与-48 V、-48-GND的电源平面有大面积的重合。这样,VTT中的时钟噪声通过容性耦合的方式耦合到-48V、-48-GND的线上,而与-48V、-48-GND直接相连的框体供电电源线成为了很好的发射天线。时钟噪声耦合到电源的原理图如图6.37所示。

【处理措施】

(1)改变主控制板电源层VTT的电源平面分布,避开-48V电源平面、使-48 V电源平面所在的区域除-48V电源及其地平面外无其他任何平面。

(2)优化VTT电源去耦电容为0.1μF和0.022 μF。

【思考与启示】

(1)PCB的入口供电电源及其相关电路应与PCB中其他的电路做好良好的隔离与去耦使电源信号相对独立,以免PCB中的信号耦合到电源信号中。

(2)对干隔离电源,既要做好电平线的隔离,也要做好“0V”线的隔离。

以上案例来自EMC领域知名专家-郑老师《EMC电磁兼容设计与测试案例分析》著作内容其一案例!

https://file1.elecfans.com/web2/M00/A4/CE/wKgZomUMN

https://file.elecfans.com/web1/M00/85/2B/pIYBAFxiNN