时间:2025-03-05 11:24

人气:

作者:admin

一前言

电子技术的进步发展使我们的生活中充满着形形色色的电子产品,LCD显示屏便是其中之一。它被广泛应用在手机、电脑、仪表、控制器等产品上,目前主流的LCD显示接口为RGB、LVDS、MIPI和HDMI。

而信号的传输阻抗是需要重点考虑的一个方面,特别是差分信号和高速率传输信号。如果信号能做好阻抗匹配,不仅可以使信号在传输线上平稳地传输,减少反射现象,提高信号的完整性和准确性,也可防止产生噪声干扰。

二阻抗匹配

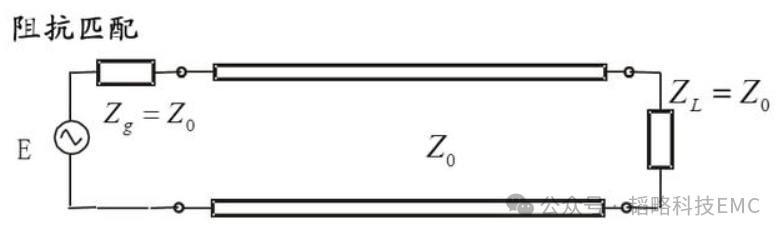

阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。

HDMI、LVDS、FPD-Link接口等高速数字接口都有严格的阻抗控制要求。通过使用特定的传输线结构(如微带线、带状线)和控制 PCB 布线的参数,可以实现特性阻抗的匹配,确保高速数字信号的稳定传输。

图1 阻抗匹配

【阻抗匹配的作用】:提高信号传输速率

1.减少串扰;

2.减少信号反射;

3.保证系统的稳定性和可靠性;

4.满足高速信号传输标准和需求。

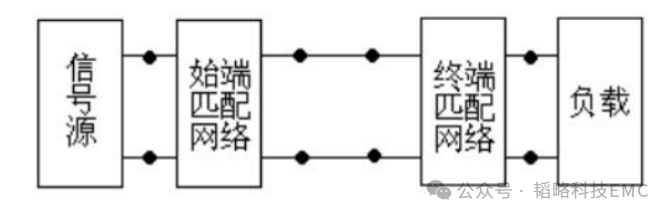

【阻抗匹配实现方法】:

1.变压器匹配;

2.串联 / 并联电阻匹配;

3.调整传输线特性阻抗。

图2 阻抗匹配的方法

三案例分析整改

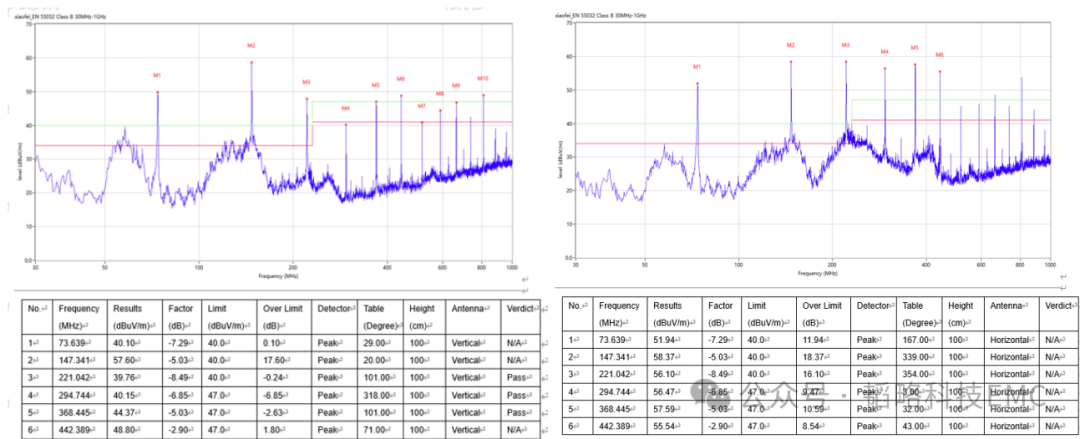

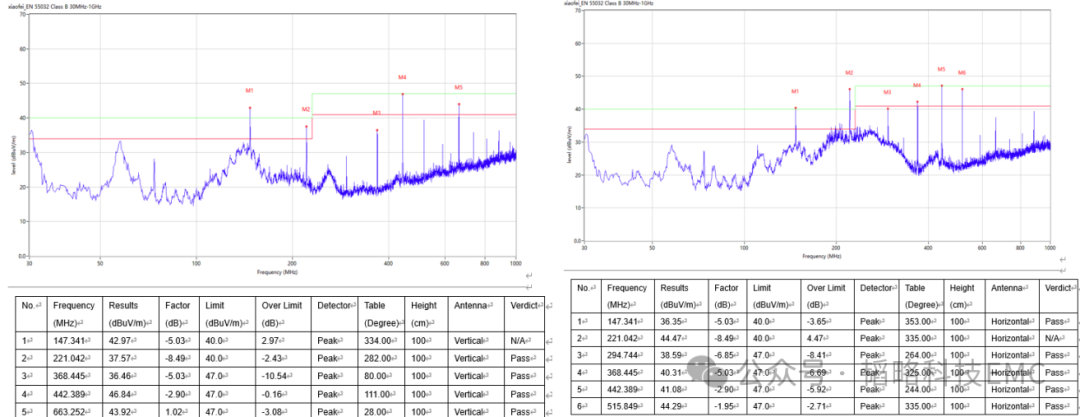

从图4中的测试数据可知问题点是时钟的倍频超标严重,根据测试数据中的时钟干扰可得出超标的基频约为73.75MHz,通过频谱仪去查找超标时钟源头,排查判定为显示屏差分信号的时钟问题。

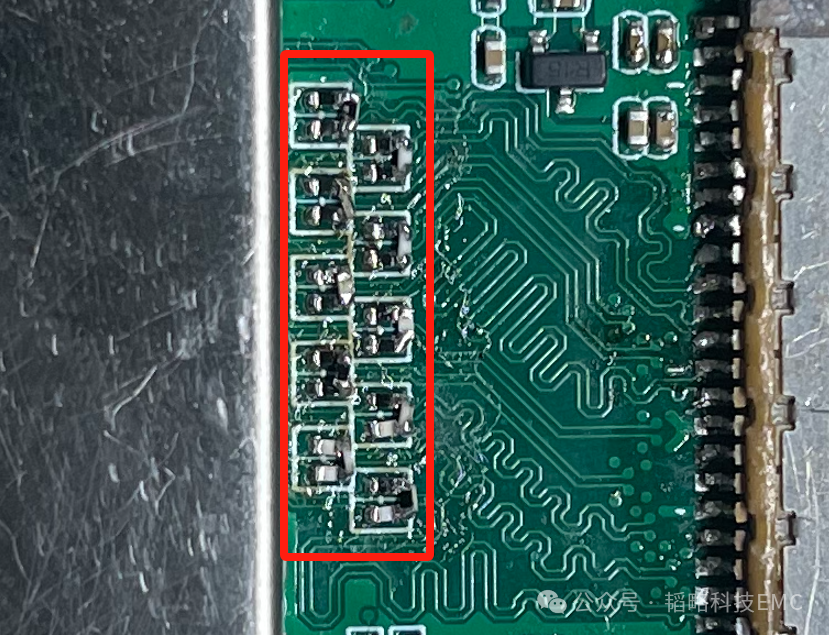

整改措施如下,在负载端差分信号之间并联100欧电阻,措施如下图所示:

图3 实际整改措施图片

加上并联电阻形成阻抗匹配后,再去看数据变化,根据测试数据可知,阻抗匹配可很大程度改善RE辐射效果,噪声降幅最大降幅达14db,如下图所示:

图4 整改前的RE测试数据

图5 整改后的RE测试数据

四总结

阻抗匹配是高速信号的一大重要点,阻抗不匹配会导致串扰,不仅会对信号完整性产生影响,也会对整个PCB形成噪声干扰,导致机器的辐射干扰超标,使其过不了EMI的测试标准。

高速率传输电路必须考虑其阻抗匹配问题,只有实现了输出阻抗与负载阻抗“完美”的匹配,才能实现信号的无反射传输,实现最大功率化利用。

https://file1.elecfans.com/web2/M00/A4/CE/wKgZomUMN

https://file.elecfans.com/web1/M00/85/2B/pIYBAFxiNN