时间:2025-05-15 14:25

人气:

作者:admin

静电放电(ESD)问题对芯片可靠性构成严峻挑战。本文介绍了芯片级ESD(HBM、CDM、MM)和系统级ESD(IEC61000-4-2)的测试标准、测试方法和测试等级,并对比分析了芯片级ESD和系统级ESD之间的差异。随后,介绍了隔离系统中常用的ESD防护设计方法和测试注意事项。

芯片级ESD测试和系统级ESD测试共同体现了芯片在整个生命周期中的抗ESD性能,但这两种参数的测试对象不同,对应的测试标准也不同。芯片级ESD测试以独立芯片作为DUT,用于评估芯片本身的抗ESD能力。而系统级ESD则是以完整产品作为DUT,用于评估整套产品对外界ESD的抗干扰能力。因此,芯片内部集成的ESD保护电路存在不足以承受同等级的系统级ESD直接冲击的可能,这也是使用系统级ESD对芯片直接进行测试更容易失效的原因。

芯片级ESD与系统级ESD测试标准介绍和差异分析技术文档免费下载:

*附件:AN-13-0009_芯片级ESD与系统级ESD测试标准介绍和差异分析.pdf

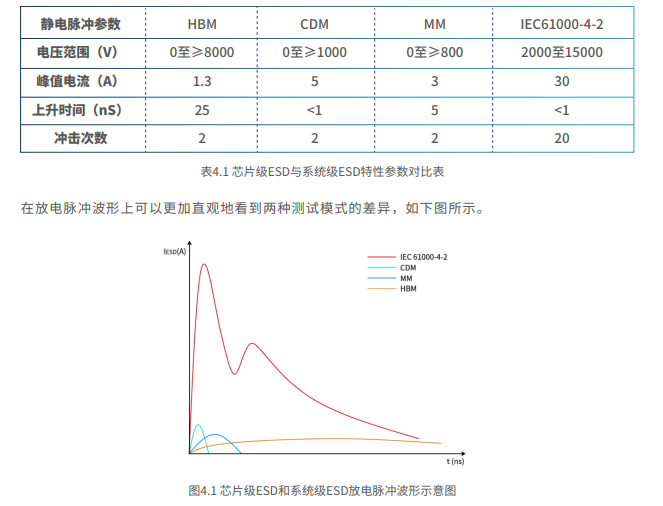

在测试方法上,芯片级ESD是在固定夹具上测试,芯片处于不上电状态。而系统级ESD的测试则是将芯片焊接在PCB上,测试过程中芯片可能处于上电状态,测试引脚组合也会因系统电路连接差 异 而 不 同 。 此 外 , 标 准 规 定 的 H B M 测 试 要 求 正 负 极 性 各 3 次 的 脉 冲 电 压 测 试 , 而 I E C61000-4-2要求至少正负极性各10次的脉冲电流测试,电荷的持续累积也会加速芯片损伤。在放电脉冲波形参数上,芯片级ESD和系统级ESD相比较,脉冲电压范围、脉冲上升时间、脉冲电压冲击次数等参数均有明显的差异,如下表所示:

可以看出,一方面,基于IEC61000-4-2标准的ESD能量远高于HBM和CDM,以8kV接触放电为例,系统级ESD脉冲电流峰值为30A,而HBM为1.3A,CDM为5A,系统级ESD相比于芯片级ESD对芯片内部的保护器件增加了6倍的电应力需求。另一方面,系统级ESD脉冲上升时间在0.7ns~1ns之间,而HBM的脉冲时间一般需要25ns,系统级ESD对芯片内部保护电路的响应时间提出了更加严格的要求,这就使得主要以HBM模型设计的保护电路无法及时响应,从而使芯片功能电路直接被损坏。

https://file1.elecfans.com/web2/M00/A4/CE/wKgZomUMN

https://file.elecfans.com/web1/M00/85/2B/pIYBAFxiNN