时间:2025-09-01 14:14

人气:

作者:admin

本系统基于米尔MYC-YM90X构建,搭载安路DR1 SOC 创新型异构计算平台,充分发挥其双核Cortex-A35与可逻辑(PL)单元的协同优势。通过AXI4-Stream总线构建的高速数据通道(峰值带宽可达12.8GB/s),实现与FPGA间的纳秒级(ns)延迟交互,较传统方案提升了3倍的传输效率,极大地提升了系统整体性能。

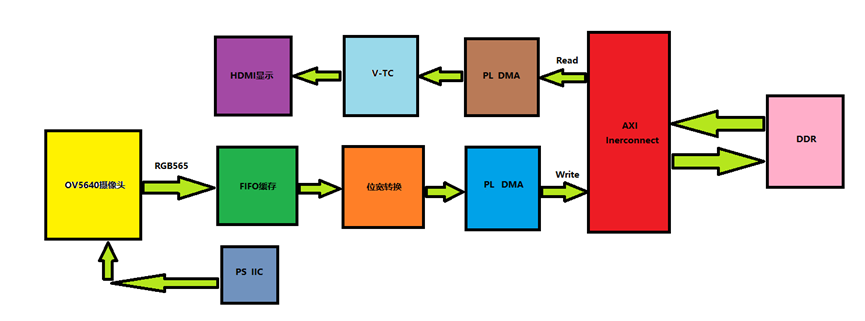

图一 系统架构框图

如图一所示,系统架构通过“低内聚,高”的设计思想,通过模块化的设计方式,完成了以下工作。

1. 通过I²C对OV5640摄像头进行分辨率,输出格式等配置。2. 双目图像数据进行三级帧缓存,FIFO————DDR。3. 客制化低延迟ISP(根据场景需求加入)

4. VTC驱动输出显示

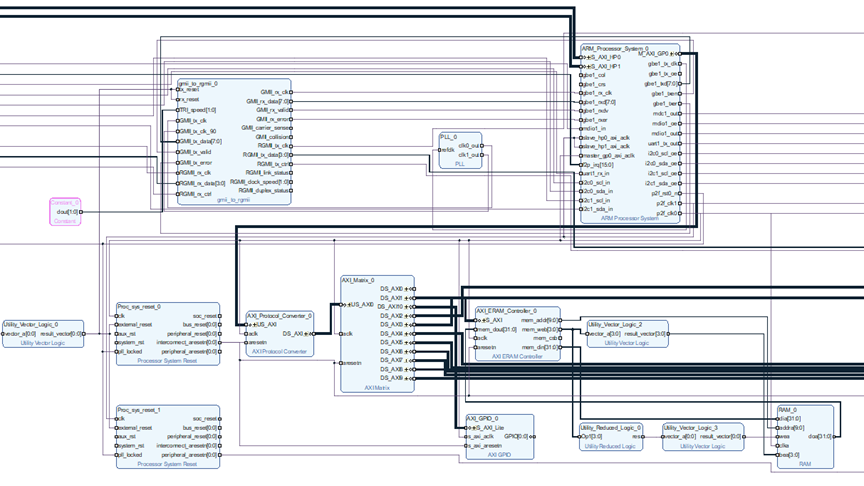

GUI设计界面,类Blockdesign设计方式,通过AXI总线,连接DR1的ARM核与定制化外设,包括,模块,PL DMA和VTC。

图二 FPGA底层架构框图

为实现高效的传感器配置,本系统采用混合式I²C配置引擎,通过PL端硬件I²C控制器实现传感器参数的动态加载。与纯软件方案相比,该硬件加速的配置速度提升了8倍,显著降低了配置延迟。

// 可重配置传感器驱动IPmodule ov5640_config (input wire clk_50M,output tri scl,inout tri a,input wire [7:0] reg_dr,input wire [15:0] reg_data,output reg config_done);// 支持动态分辨率切换(1920x1080@30fps 1280x720@60fps)parameter [15:0] RESOLUON_TABLE[4] = '{...};

该配置引擎支持多分辨率与高帧率动态切换,适应不同应用场景需求。

系统构建了三级缓存体系,确保数据处理的高效性和实时性:

// 位宽转换适配器module data_width_converr #(parameter IN_WIDTH = 16,parameter OUT_WIDTH = 96)(input wire [IN_WIDTH-1:0] din,output wire [OUT_WIDTH-1:0] dout,// 时钟与使能);// 采用流水线式位宽重组技术always_ff @(posedge clk) begincase(state)0: buffer <= {din, 80'b0};1: buffer <= {buffer[79:0], din};// ...6周期完成96bit组装endcaseend

系统通过AXI-DMA(Direct Memory cess)实现零拷贝数据传输,优化内存和外设间的数据交换:

axi_hdmi_tx#(.ID(0),.CR_CB_N(0),.DEVICE_TYPE(17), // 17 for DR1M.INTERFACE("16_BIT"),.OUT_CLK_POLARITY (0))axi_hdmi_tx_inst (.hdmi_clk (pll_clk_150),//.hdmi_clk (clk1_out),.hdmi_out_clk (hdmi_clk ),.hdmi_16_hsync (hdmi_hs ),.hdmi_16_vsync (hdmi_vs ),.hdmi_16_data_e (hdmi_de),.hdmi_16_data (/hdmi_data/ ),// .hdmi_16_data (hdmi_data ),.hdmi_16_es_data (hdmi_data),.hdmi_24_hsync (),.hdmi_24_vsync (),.hdmi_24_data_e (),.hdmi_24_data (/{r_data,g_data,b_data}/),.hdmi_36_hsync (),.hdmi_36_vsync (),.hdmi_36_data_e (),.hdmi_36_data (),.vdma_clk (pll_clk_150 ),.vdma_end_of_frame (dma_m_axis_last ),.vdma_valid (dma_m_axis_valid ),.vdma_data (dma_m_axis_data ),.vdma_ready (dma_m_axis_ready),.s_axi_aclk (S_AXI_ACLK ),.s_axi_aresetn (S_AXI_ARESETN ),.s_axi_awvalid (axi_ds5_ds5_awvalid ),.s_axi_awaddr (axi_ds5_ds5_awaddr ),.s_axi_awprot (axi_ds5_ds5_awprot ),.s_axi_awready (axi_ds5_ds5_awready ),.s_axi_wvalid (axi_ds5_ds5_wvalid ),.s_axi_wdata (axi_ds5_ds5_wdata ),.s_axi_wstrb (axi_ds5_ds5_wstrb ),.s_axi_wready (axi_ds5_ds5_wready ),.s_axi_bvalid (axi_ds5_ds5_bvalid ),.s_axi_bresp (axi_ds5_ds5_bresp ),.s_axi_bready (axi_ds5_ds5_bready ),.s_axi_arvalid (axi_ds5_ds5_arvalid ),.s_axi_araddr (axi_ds5_ds5_araddr ),.s_axi_arprot (axi_ds5_ds5_arprot ),.s_axi_arready (axi_ds5_ds5_arready ),.s_axi_rvalid (axi_ds5_ds5_rvalid ),.s_axi_rresp (axi_ds5_ds5_rresp ),.s_axi_rdata (axi_ds5_ds5_rdata ),.s_axi_rready (axi_ds5_ds5_rready));

// VTC配置代码片段(An SDK)void config_vtc(uint32_t h_total, uint32_t v_total) {VTCRegs->CTRL = 0x1; // 使能软复位VTCRegs->HTOTAL = h_total - 1;VTCRegs->VTOTAL = v_total - 1;// 详细时序参数配置VTCRegs->POLARITY = 0x3; // HS/VS极性配置VTCRegs->CTRL = 0x81; // 使能模块}

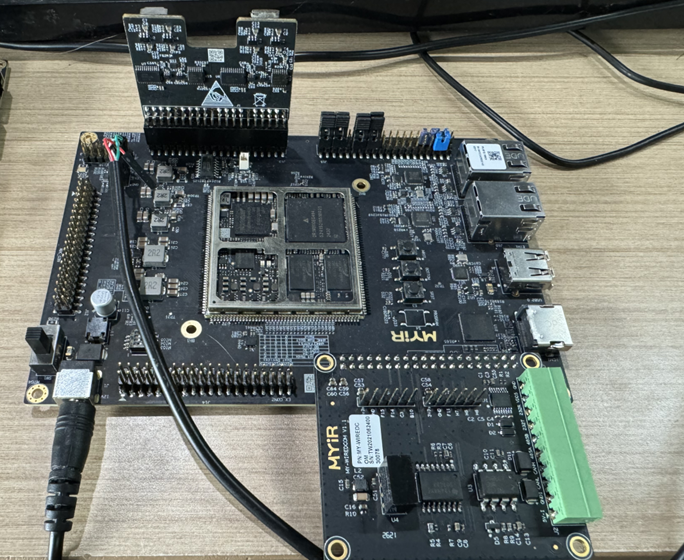

米尔的安路飞龙板卡采用2 X 50 N 设计,可灵活插拔多种子卡,配合子卡套件,可扩展成多种形态,多种应用玩法。

图三 使用模组,底板,子卡和线缆搭建硬件系统

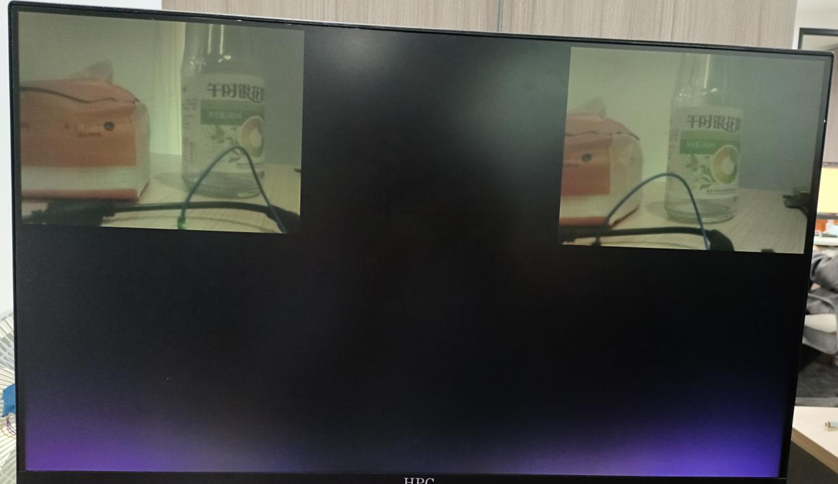

实测双目显示清晰,无卡帧,闪屏。

图四 输出显示效果

三路DMA设备树HDMI、camera1、camera2代码片段:

//hdmisoft__dma0: dma@80400000 {compatible = "adi,axi-dmac-1.00.a";reg = <0x0 0x80400000 0x0 0x10000>;interrupts = ;clocks = <&axi_dma_clk>;#dma-cells = <1>;status = "okay";adi,channels {#size-cells = <0>;#address-cells = <1>;dma-channel@0 {reg = <0>;adi,source-bus-width = <32>;adi,source-bus-type = <0>;adi,destination-bus-width = <64>;adi,destination-bus-type = <1>;};};};// cam1mipi_adi_dma0: dma@80300000 {compatible = "adi,axi-dmac-1.00.a";reg = <0x0 0x80300000 0x0 0x10000>;interrupts = ;clocks = <&axi_dma_clk>;#dma-cells = <1>;status = "okay";adi,channels {#size-cells = <0>;#address-cells = <1>;dma-channel@0 {reg = <0>;adi,source-bus-width = <128>;adi,source-bus-type = <1>;adi,destination-bus-width = <64>;adi,destination-bus-type = <0>;};};};//caipi_adi_dma1: dma@80700000 {compatible = "adi,axi-dmac-1.00.a";reg = <0x0 0x80700000 0x0 0x10000>;interrupts = ;clocks = <&axi_dma_clk>;#dma-cells = <1>;status = "okay";adi,channels {#size-cells = <0>;#address-cells = <1>;dma-channel@0 {reg = <0>;adi,source-bus-width = <128>;adi,source-bus-type = <1>;adi,destination-bus-width = <32>;adi,destination-bus-type = <0>;};};};

双路OV5640设备树配置代码片段

camera@3c { compatible = "ovti,ov5640"; pinctrl-names = "default"; // pinctrl-0 = <&pinctrl_ov5640>; reg = <0x3c>; clocks = <&ov5640_clk>; clock-names = "xclk"; // DOVDD-supply = <&vgen4_reg>; /* 1.8v / // AVDD-supply = <&vgen3_reg>; / 2.8v / // DVDD-supply = <&vgen2_reg>; / 1.5v / powerdown-gpios = <&portc 8 GPIO_ACTIVE_HIGH>; reset-gpios = <&portc 7 GPIO_ACTIVE_LOW>; port { / Parallel bus endpoint / ov5640_out_0: endpoint { remote-endpoint = <&vcap_ov5640_in_0>; bus-width = <8>; data-shift = <2>; / lines 9:2 are used */ hsync-active = <0>; vsync-active = <0>; pclk-sample = <1>; }; }; };

性能实测数据。

| 指标 | 实测值 | 理论峰值 |

| 图像处理延迟 | 18.7ms | ≤20ms |

| DDR吞吐量 | 2GB/s | 2.6GB/s |

| 功耗(全负载) | 3.8W | 4.2W |

| 启动时间(Linux) | 18s | - |

该方案可广泛应用于以下领域:

通过安路TD 2024.10开发套件,开发者能够快速移植和定制化开发,具体包括:

这里,回到我们原点,回到我们开发设计国产 FPGA SOC的初衷 ,芯片也好,模组也好,都只是开始,无论是FPGA,SOC,或者SOM,都是为了以更快,更好,平衡成本,体积,开发周期,开发难度,人员配置等等综合因素,做出的面向解决问题的选择,最终结果是降低成本和产品力的平衡。

安路飞龙系列的问世,让我们很欣喜看见国产SOC FPGA的崛起,希望和业界开发者一起开发构建国产SOC FPGA生态,所以选择将系列以知识库全部开源,共同无限进步!

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有