时间:2025-05-28 10:54

人气:

作者:admin

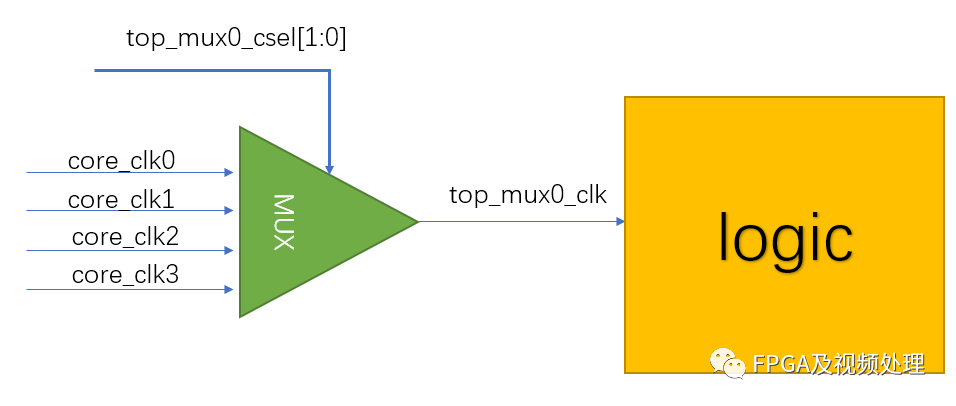

在trion要实现一个4选1复用或许比较麻烦。但是在钛鑫上已经给出了解决方案。这里以60F225为例来介绍如何实现下面的4选择1时钟选择功能。

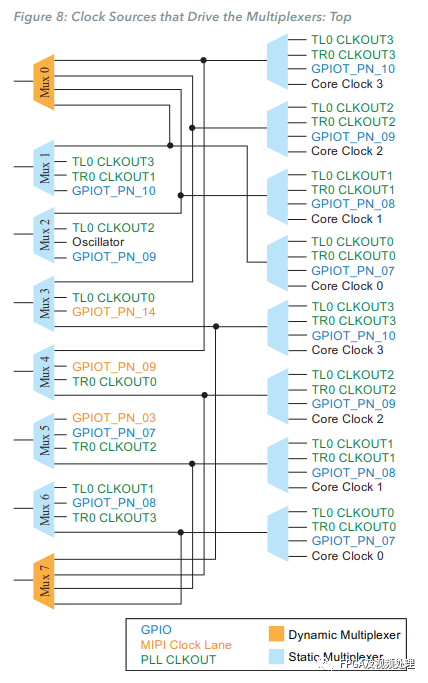

在的top,bottom,right和left各有8个clkmux,分别是Mux 0 ~ Mux 7。

每个MUX的时钟来源包括GO,LVDS RX(支持gclk和rclk),MIPI RX LANE(用于时钟的),PLL,Oscillator(片上晶振)和Core(从Core逻辑出来的)

其中只有Mux0和Mux7可以支持4路动态复用,相当于的clockctrl模块用于时钟动态选择。下图以top为例。

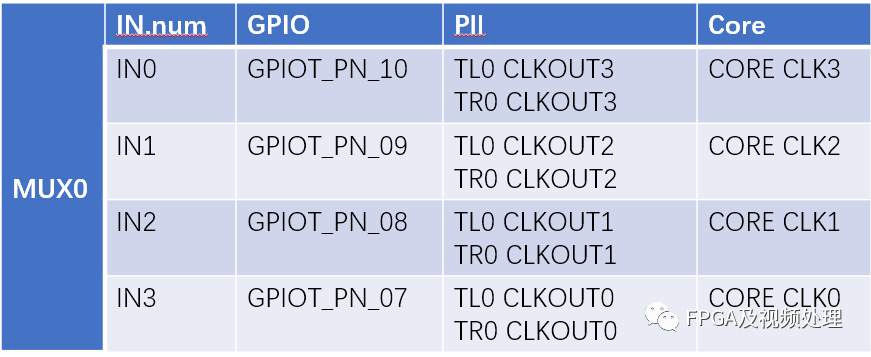

从上图我们可以看到MUX0和MUX7的时钟来源包括Core Clock,GPIO,PLL。我们详细列出top部分Mux0的时钟源。如表1

表1

有了上面的信息,我们来进行关于时钟复用的设置。

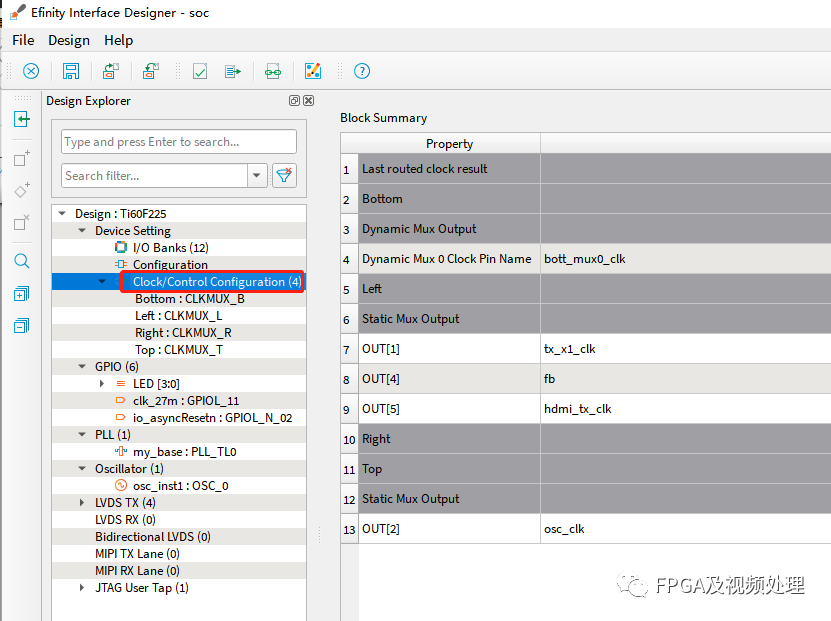

在interface中选择Device Setting -> Clock/Control Configuration,可以看到对应的top,bottom,right和left的选项。

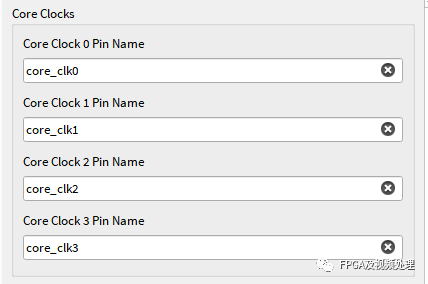

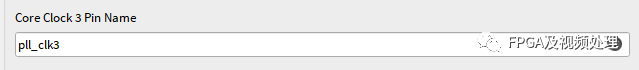

这里我们点击Top:CLKMUX_T,在右侧Global Buffe可以看到三部分。分别是Core Clocks, Enable Dynamic Mux0和Enable Dynamic Mux7(前面已经提到只有Mux0和Mux7支持动态复用)。 对于表1中的Core clocks就是在下图的Core Clocks设置。它指由Core 到interface中的信号。该信号如果是Core中有逻辑信号需要添加相应的GPIO。这里分别命名为core_clk0,core_clk1,core_clk2和core_clk3. 对于GPIO和PLL的时钟并不需要手动输入,因为是固定的时钟,只需要选择即可(如果不明白,请继续往下看)。

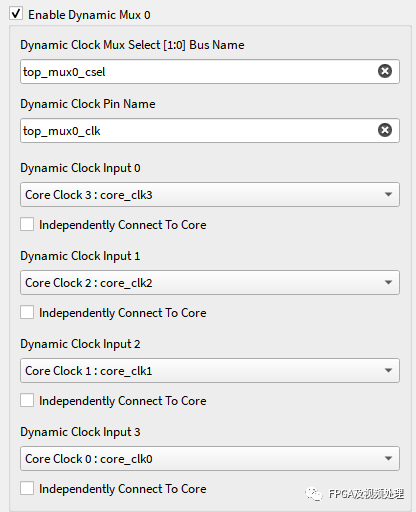

这里我们只打开Mux0,即勾选Enable Dynamic Mux0。

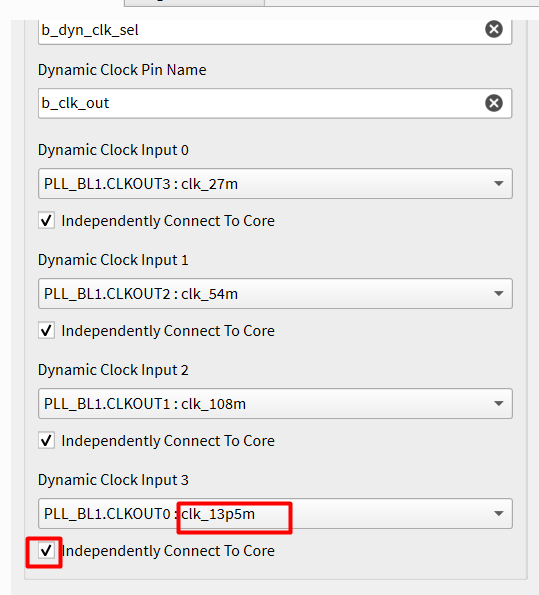

Dynamic Clock Mux Select[1:0] Bus Name是选择信号的名称,这里我们输入top_mux0_csel;

Dynamic Clock Pin Name是指Mux输出的信号,这是我们命名为top_mux0_clk;

Dynamic Clock Input n(0~3):是指每个输入选择项的时钟来源。

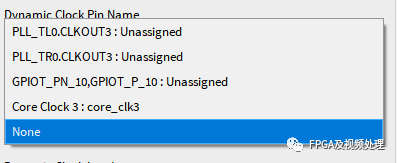

在Dynamic Clock Input N(N指0~3)下面的下拉框可以看到GPIO时钟源、PLL时钟源和Core时钟源是可以选择的。如果不需要配置该时钟可以选择None。Usigned表示相应的时钟并没有设置。根据需要选择相应的时钟即可,这里我们都选择了core_clock。

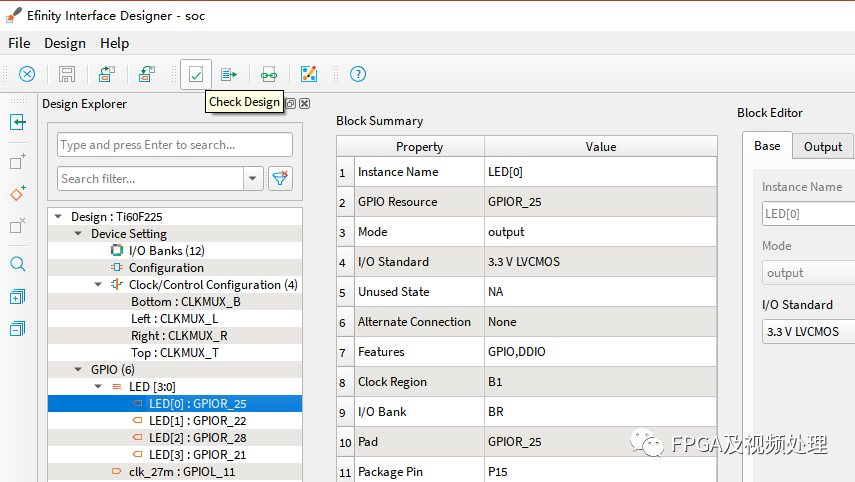

设置完成之后点击Check Design来检测设置是否有错。

Check Design无误后可以在生成的mplate中看到下面的信号,添加到顶层文件可以使用。

output[1:0]top_mux0_csel,inputtop_mux0_clk,

我们设置成如下时钟方案,在使用中报出如下错误:

Rule:clkmux_rule_core_clock_static_mux(Error)

Description:Core clock pin

说明:从core给出的core clock是不能驱动静态的MUX的,只能驱动动态MUX.包括在Core Clocks输入了从core输出的时钟,但是实际没有使用。如下图,输入了core clock名为test_clk1,但是实际使用的是PLL_TL0.CLKOUT1:tx_x1_clk,就会报上面的错误。

我们设置成如下方案,使用中可能会报如下错误:

Rule:clock_rule_dyn_clkmux_input

Description:The following clocks need to connect independently to core since they are dynamic clock mux input that also drives the clock pins on the periphery through clockout interface tx_x1_clk

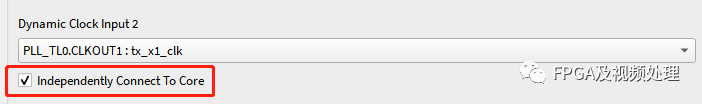

说明:这个问题是说tx_x1_clk即驱动动态的MUX,又驱动core内部的逻辑,这里需要勾选Indepndetly Connect to Core.

另外如果mux的时钟既有来自core的也有来自PLL的会给出如下警告:

Rule:clkmux_rule_pll_clock(warning)

Description:Dynamic clock mux 0 connected to both inverting and non-inverting clock sources:Clock inversion will not be applied to to_mux0_clk

说明:如果时钟来源既有core clock又有pll输出,会有上面的告警信息。

也可以把pll输入时钟输入Core Clock选项中,在时钟选择框中选择Core Clock。就不需要勾选Indepndetly Connect to Core.

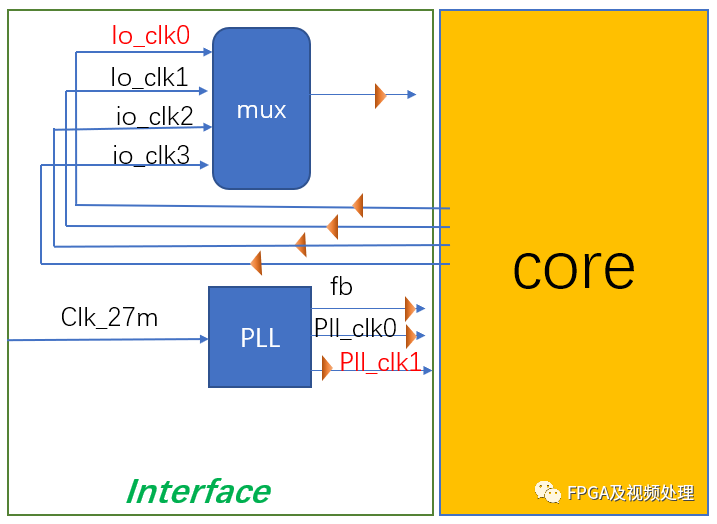

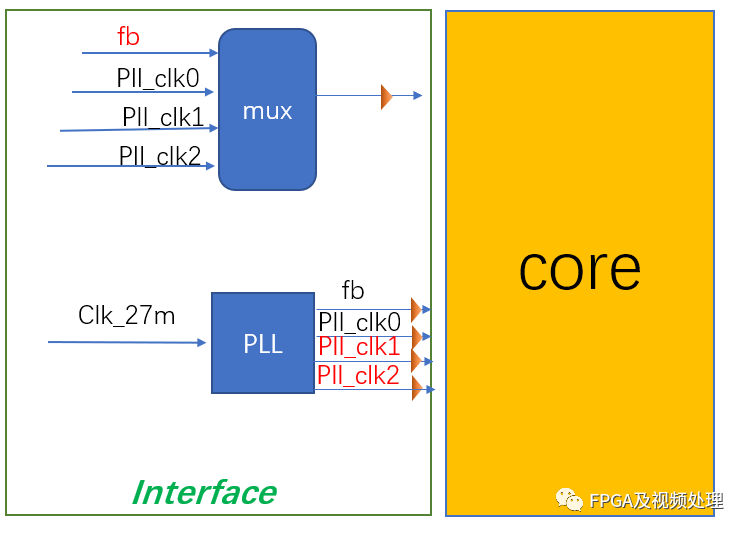

那区别在哪里呢,区别就在于如果选择pll时钟输出,时钟是在interface给到MUX的;如果选择core clock,那么时钟就要先进入core,然后再返回到interface再给到MUX,所占用的GBUF数量是不相同的.或者用另一种表达方式:core时钟进入动态MUX的信号必须要先经过GBUF,而pll的输出可以不经过GBUF而送给动态MUX.而有时候我们会发现pl给动态MUX的时钟占用了F,那是因为该时钟驱动了core逻辑。

注意

(1)如果mux的4路输入时钟没有完全选择,比如只用到两个时钟,那么输入0必须使用,否则不能运行,比如选择的是2,3两路,时钟是没有输出的;

(2)如果某一路没有时钟,也不能进行选择,否则无时钟输出也不能再切回来。比如只有0和1有时钟,选择时切到2上,肯定没有输出,再切回0或者1也没有办法再输出。

(3)如果没有勾选Independently Connect To Core,即使逻辑顶层定义了该时钟也是不能使用的。

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有