时间:2023-12-06 09:14

人气:

作者:admin

什么是帧缓存(frmbuf)

在视频处理系统中,将输入的图像以帧为单位储存到存储器(DDR)中,再根据输出时序需求,读取图像并输出,达到帧率变换、暂停显示的目的。

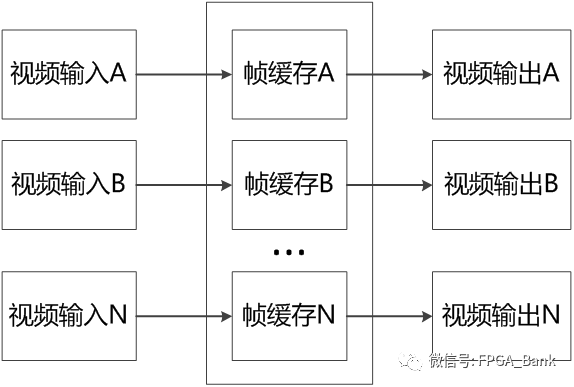

在大部分应用中,视频输入输出的数量通常都不止一组,也就是需要多个帧缓存进行视频的存储;

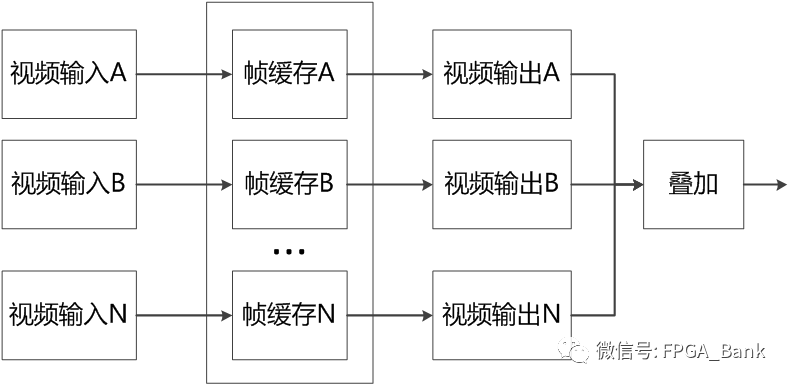

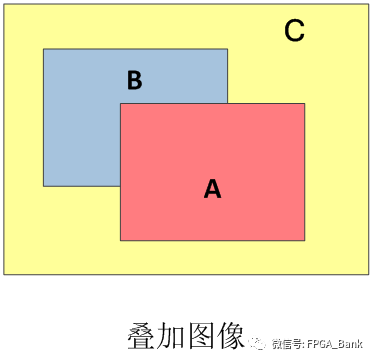

如果一个系统中存在多路视频输入,而只有一路视频输出,那么通常在帧缓存后还要将多路视频叠加在一起才可以进行输出;

常用的帧缓存设计

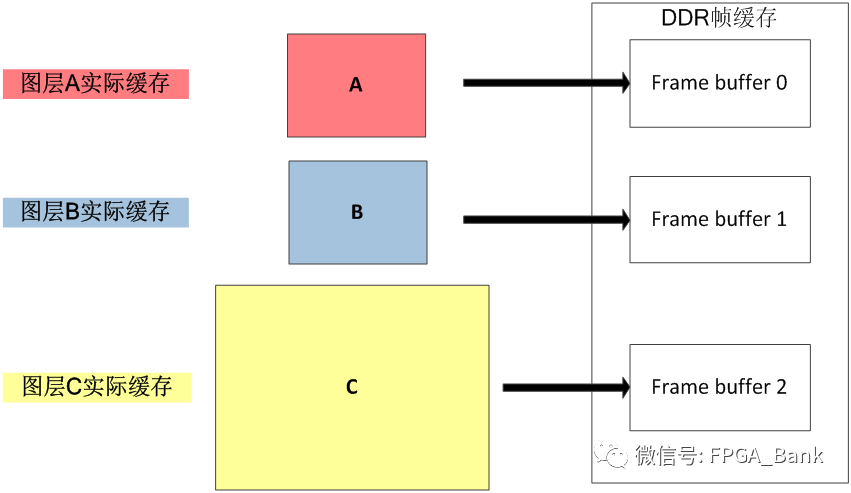

在常规的视频处理平台中,为了实现多路视频的任意叠加,会将输入到系统中的所有视频都缓存到DDR中,进行叠加时,将所有图层的完整视频从DDR读出,再根据层叠关系进行叠加;

优点:

操作简单

更改叠加位置时可以立刻响应

可拓展透明叠加功能

缺点:

每一个图层都缓存完整的视频,占用的DDR带宽较大,尤其 是在多图层系统中。

以FPGA实现存储4K@60输入,4K@60输出的视频为例:RGB444 24BIT像素

写有效带宽:3840*2160*24*60大约为12Gbit

读有效带宽:3840*2160*24*60大约为12Gbit

总的需要占用DDR带宽为24Gbit。

审核编辑:刘清

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有