时间:2023-10-01 09:49

人气:

作者:admin

本文开源一个FPGA项目: USB3.0 LoopBack 。基于FPGA的USB3.0通信方案有很多,其中非常好用的一款USB3.0芯片是 FT600/601Q 。

下面介绍一下这款FT600/601Q芯片的技术参数,控制信号、数据读写时序等,并利用官方提供的上位机软件进行数据回环测试。

FT600/601Q芯片

芯片技术参数

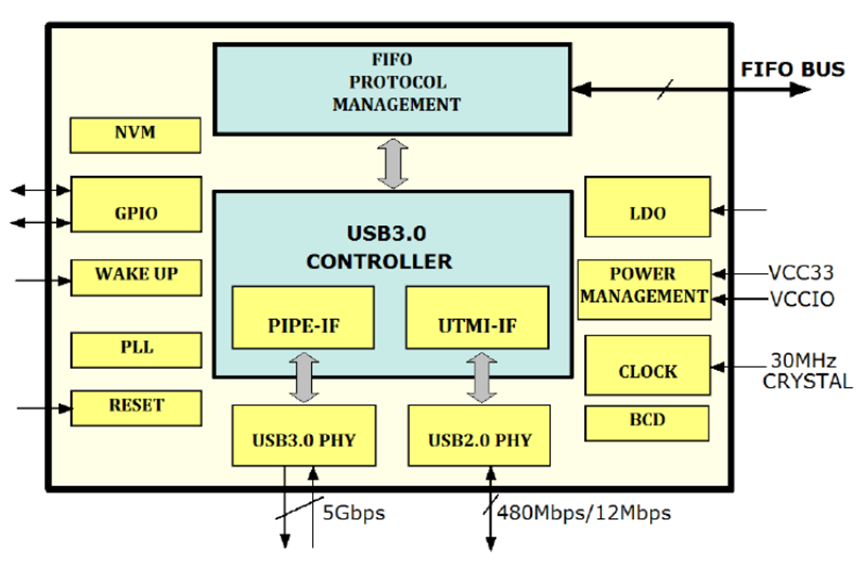

芯片内部架构

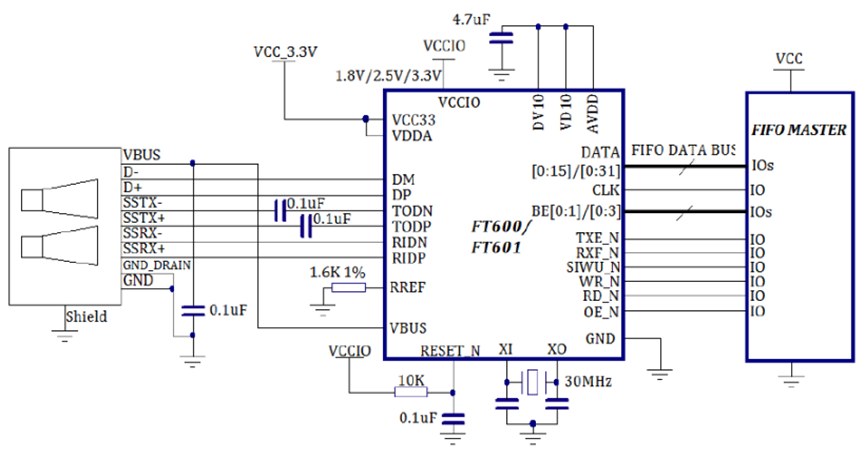

极简外围电路设计

读写模式&时序

FT600/601Q常用读写模式为245 Synchronous FIFO模式和Multi Channel FIFO模式,本工程以芯片默认的245 Synchronous FIFO模式为例。

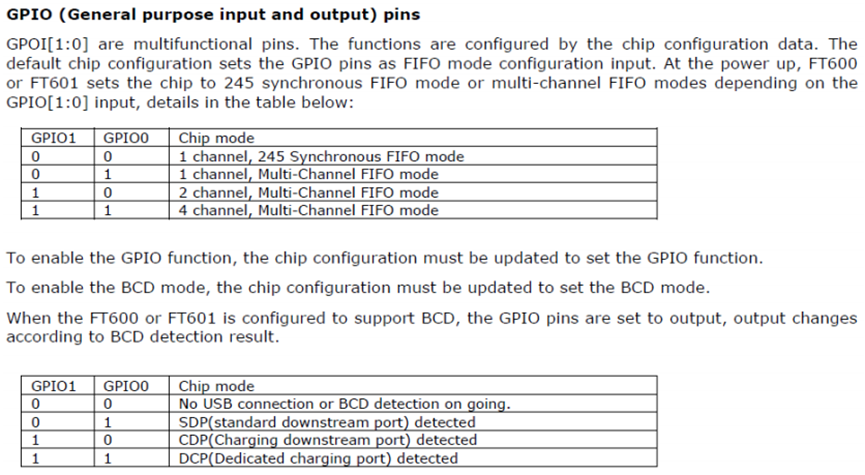

FT600/601Q读写模式是通过GPIO0和GPIO1进行配置,具体配置方法如下图所示:

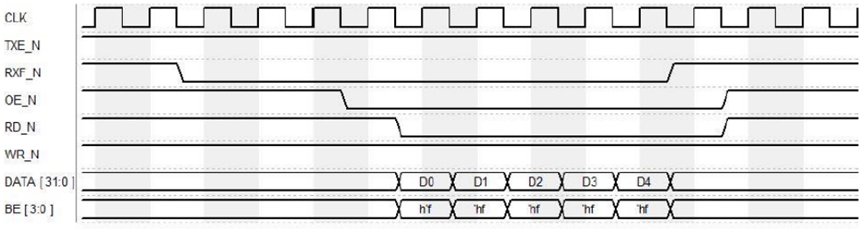

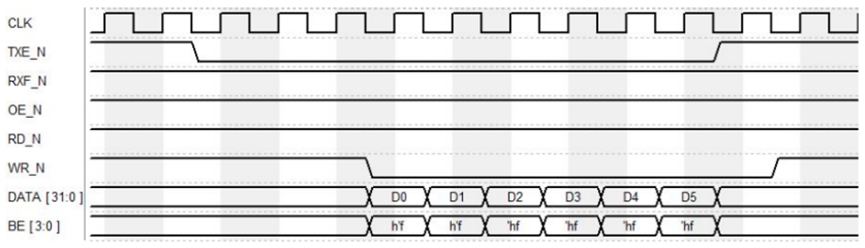

245 Synchronous FIFO模式读写时序也非常简单,当RXF_N信号拉低时, 通知FPGA开始读任务,当TXE_N信号拉低时,通知FPGA开始写任务:

回环传输测试

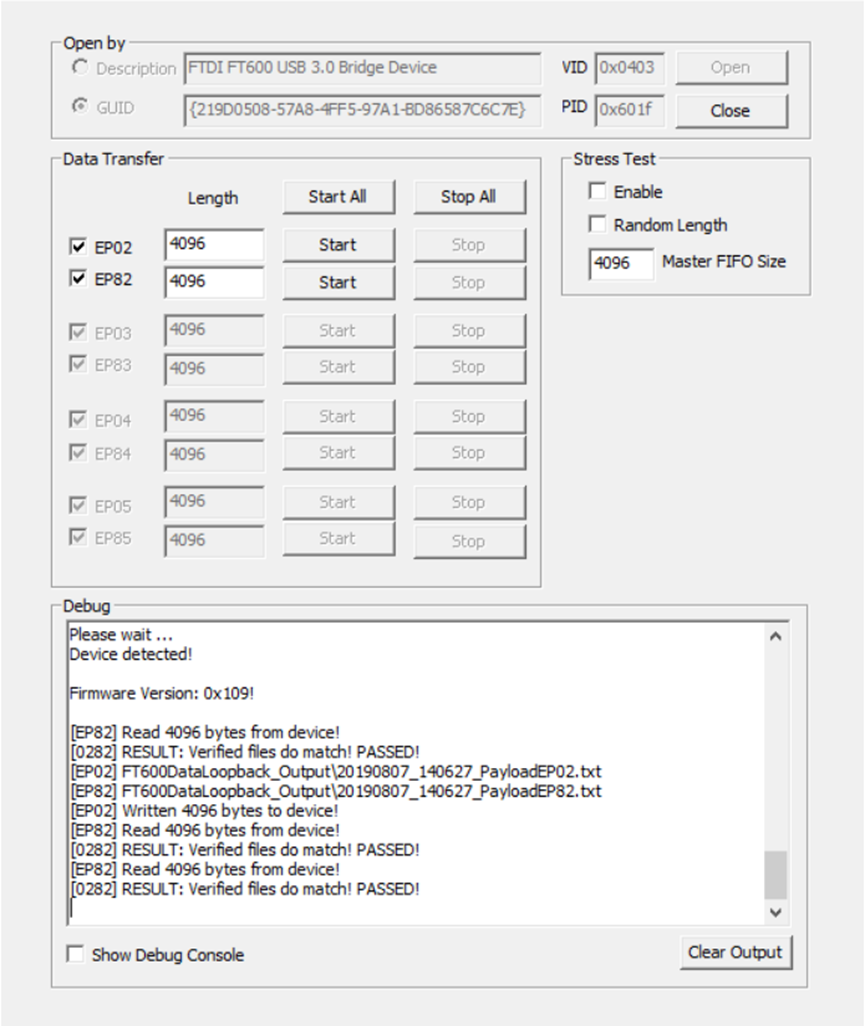

采用官方提供的FT600 Data Loopback Demo App上位机软件进行 数据回环测试 ,每次读写4096字节数据,结果如下图所示:

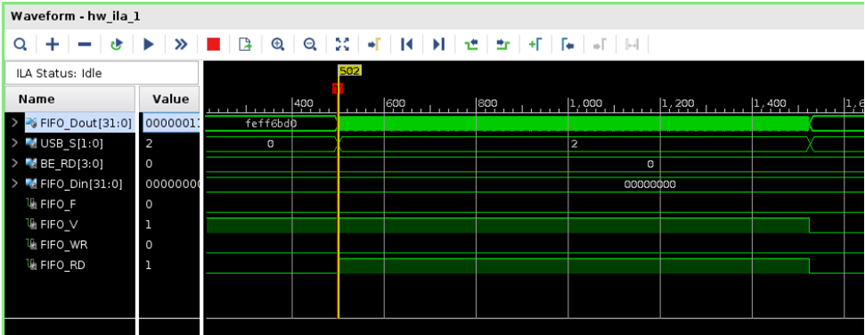

在Vivado工程中通过添加在线逻辑分析仪模块查看相关信号:

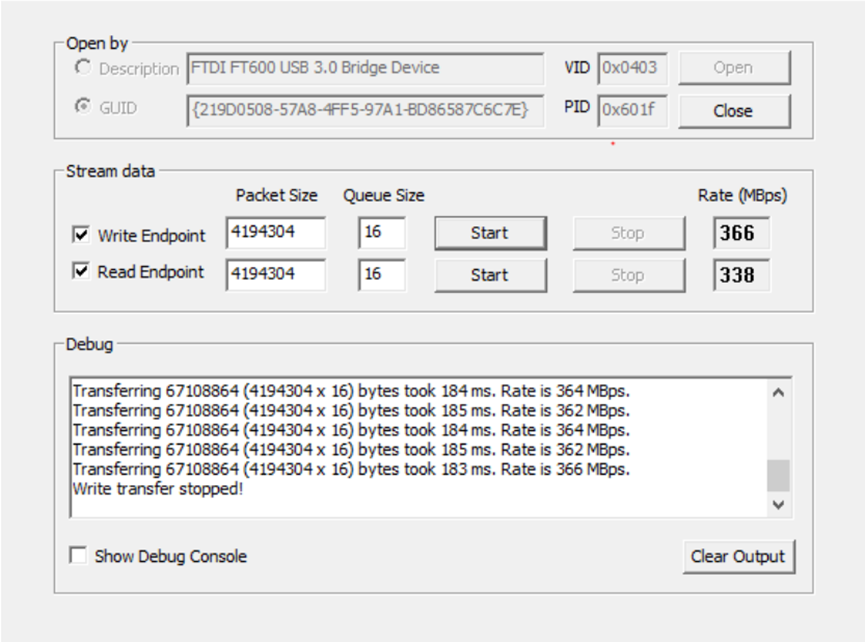

另外,还可以采用官方提供的FT600 Data Streamer Demo App上位机软件进行Stream数据流传输测试,速度可以达到360MB/S左右:

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有