时间:2019-07-31 14:50

人气:

作者:admin

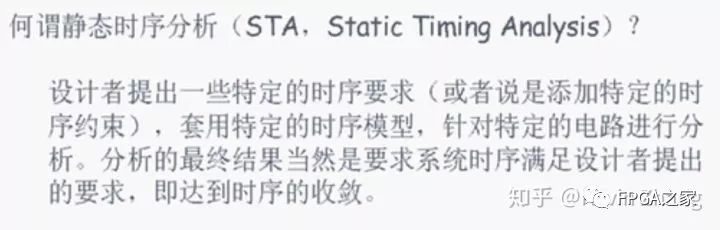

什么是静态时序分析?

通俗来说:在输入信号到输出信号中,因为经过的传输路径、寄存器、门电路等器件的时间,这个时间就是时序。开发工具不知道我们路径上的要求,我们通过时序约束来告诉开发工具,根据要求,重新规划,从而实现我们的时序要求,达到时序的收敛。

我们对整个设计添加时序约束,让整个设计。

时序的欠约束:约束的少了;

时序的过约束:约束了过了;

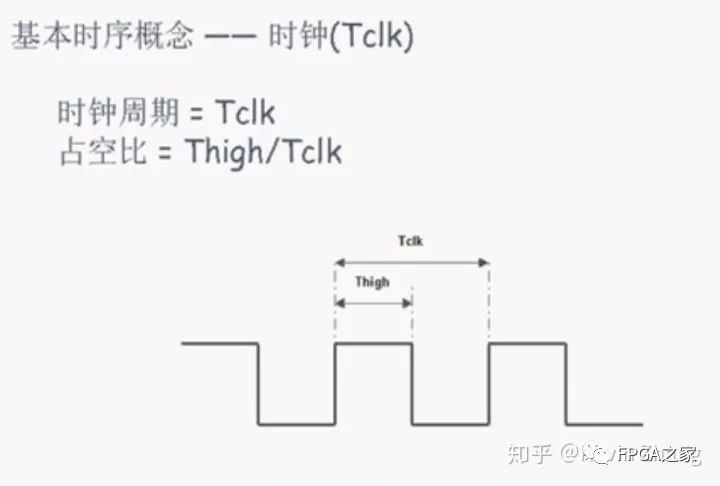

时序基本概念:时钟

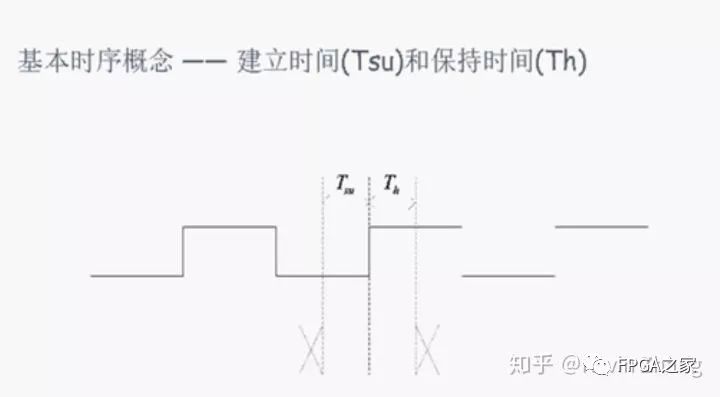

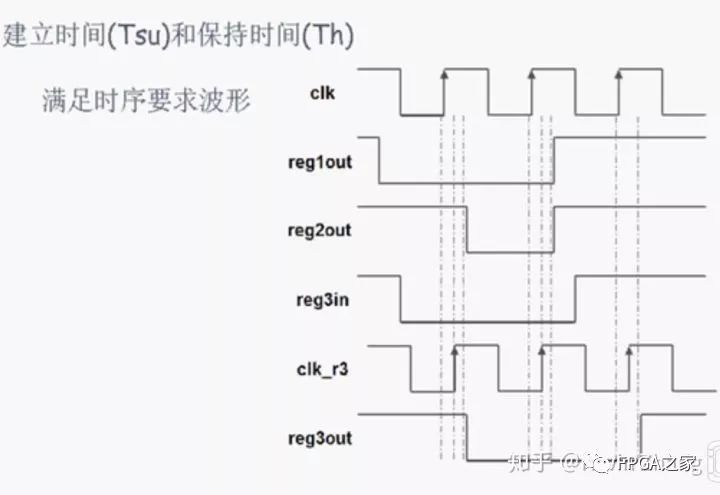

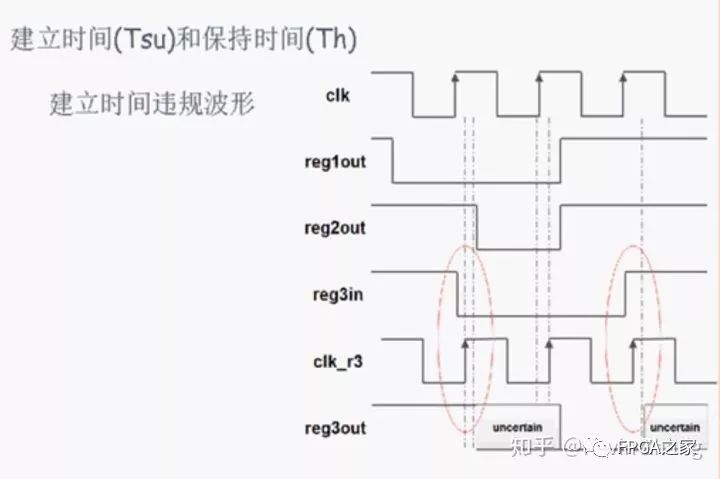

建立时间setup和保持时间hold

建立时间:在时钟上升沿前,数据不能改变的最小时间;

保持时间:在数据上升沿后,数据不能改变的最小时间;

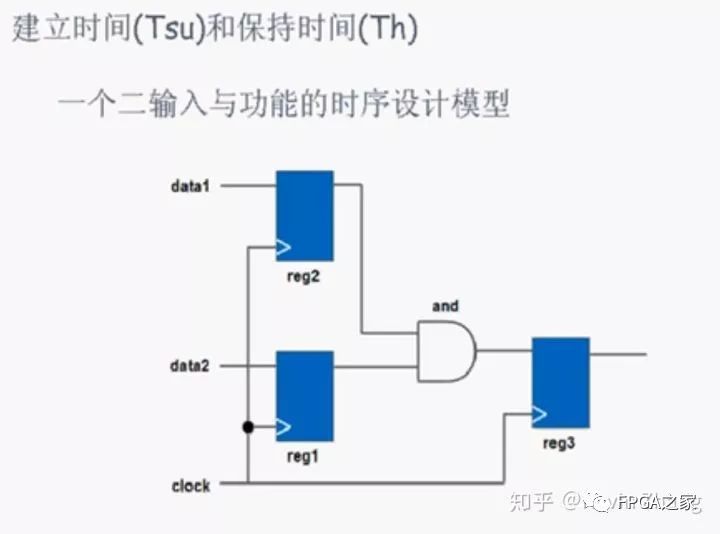

例子

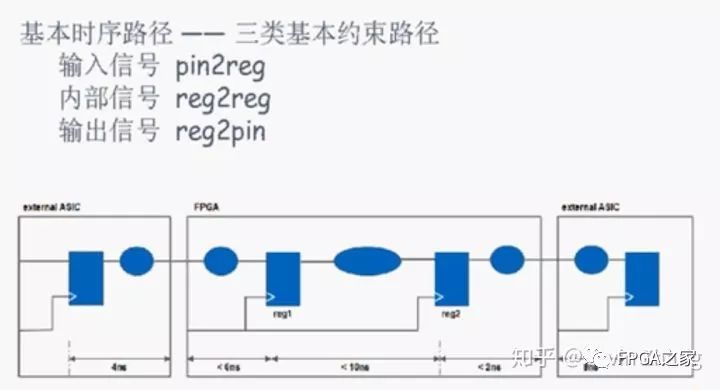

三种时序路径

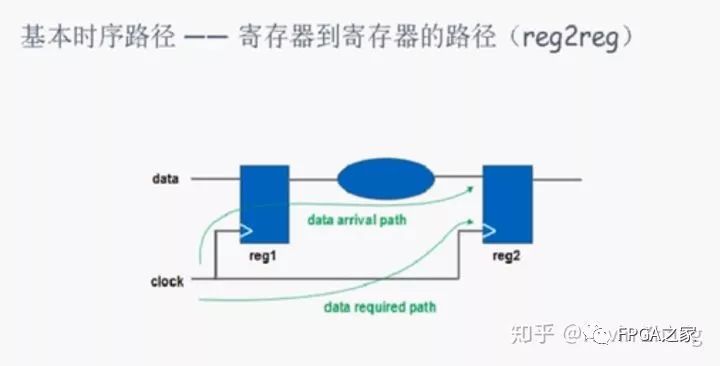

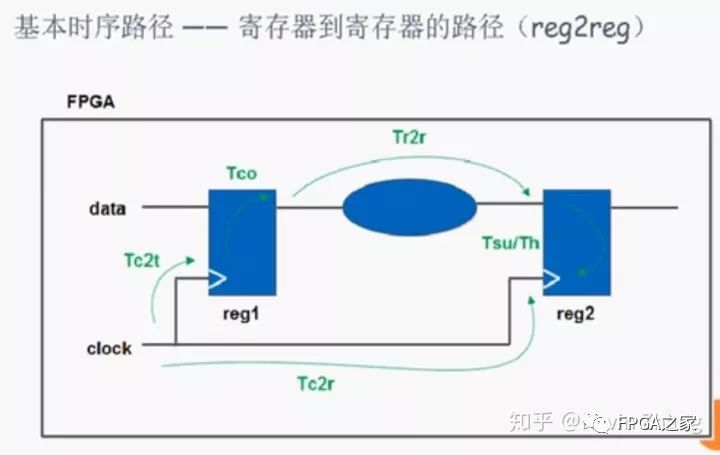

分析一个寄存器的延时

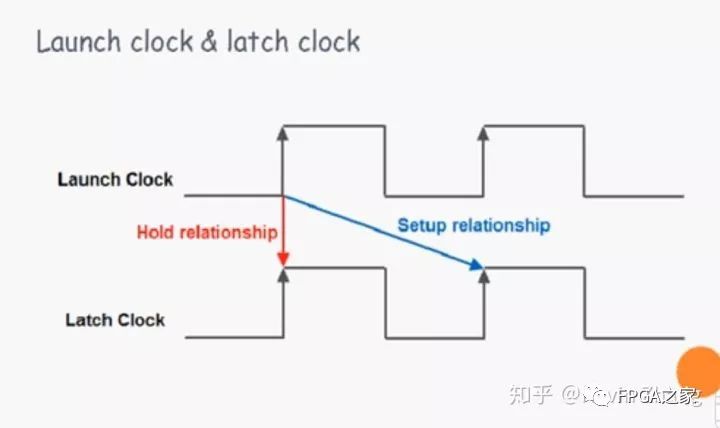

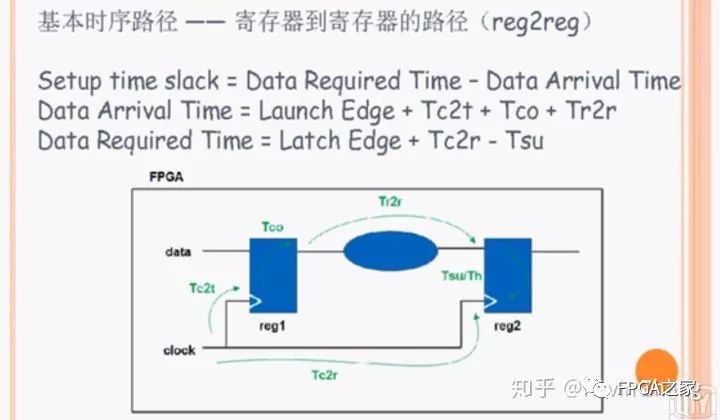

setup slack余量,这个时间是差了一个时钟周期;

数据达到时间,首先是发射时钟+时钟到REG1的延时+reg1的延时+传输路径的延时

数据时间需求:锁存时钟+时钟到reg2的延时-setup时间

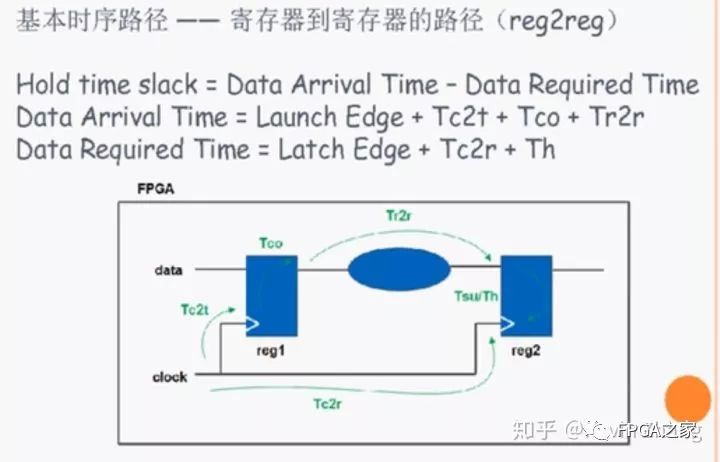

hold时间余量,这里分析的应该是同一个周期里面的时间,这个时间是对齐的;

上一篇:FPGA中循环冗余校验的不同类型

下一篇:简谈基于FPGA的千兆以太网

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有