时间:2018-06-18 19:24

人气:

作者:admin

设计背景:

随机存取存储器(random access memory,RAM)又称作"随机存储器",是与CPU直接交换数据的内部存储器,也叫主存(内存)。它可以随时读写,而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储媒介。

存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关的存储器。这种存储器在断电时将丢失其存储内容,故主要用于存储短时间使用的程序。 按照存储单元的工作原理,随机存储器又分为静态随机存储器(英文:Static RAM,SRAM)和动态随机存储器(英文Dynamic RAM,DRAM)。

设计原理:

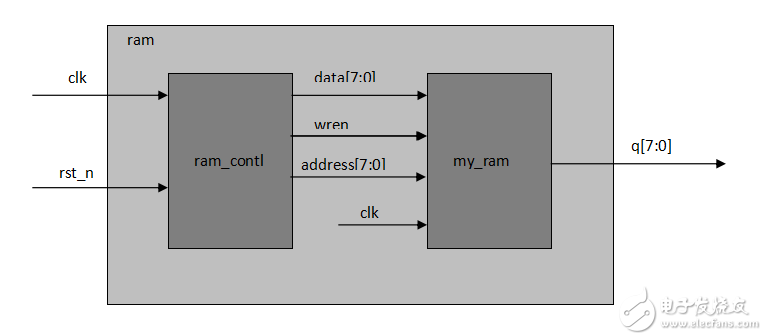

本次设计我们通过调用我们的RAM的IP核来给它写我们的控制器,来实现RAM的可读可写的特点。

我们设计的是RAM的深度为256,我们先写256个数,然后再读出我们写的256个数。值得一说的是,我们的读写标志是高位为写标志,低位为读标志。

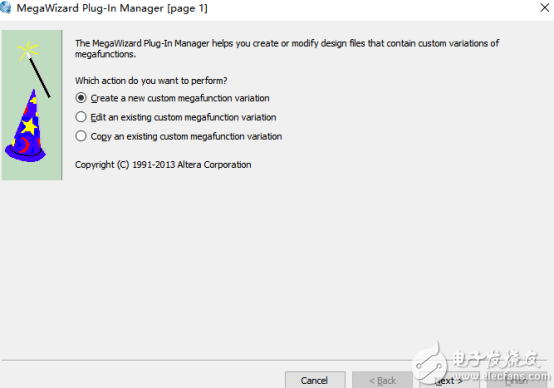

设计步骤,打开我么的调用IP核的界面,然后下一步:

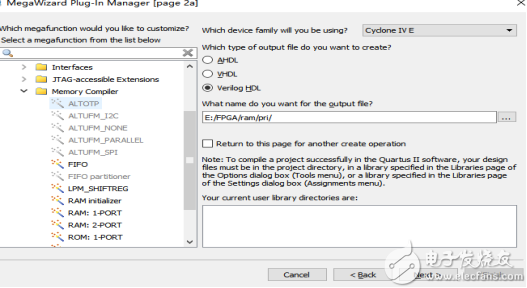

在下面的选项中选出我们RAM,如图所示,然后起一个我们的输出名,然后下一步:

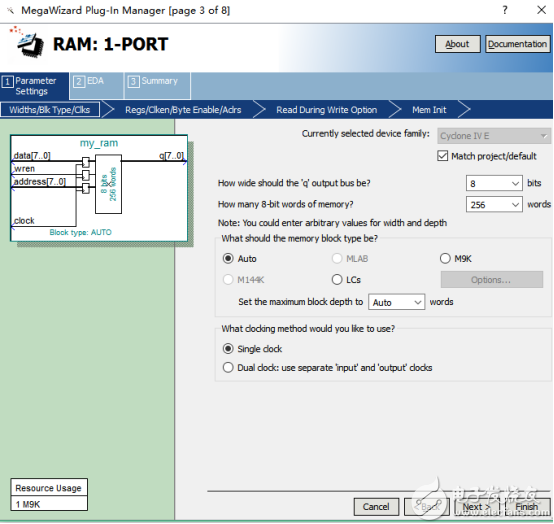

在下面的页面中我们设置我们的位宽和深度,然后设置如下,下一步:

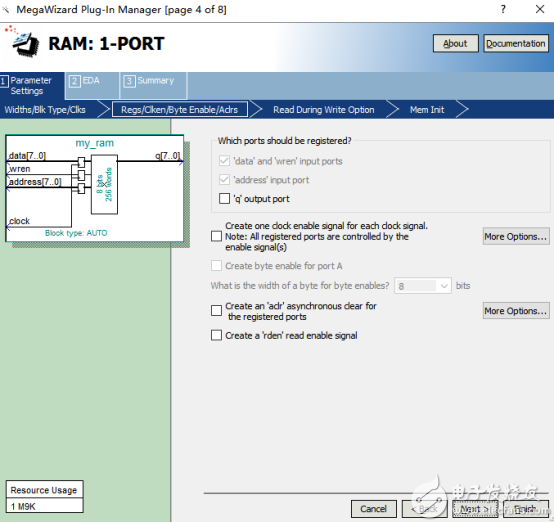

下面的页面中,问我们设置不设置我们的输出寄存器,我们不要设置,如下,然后下一步:

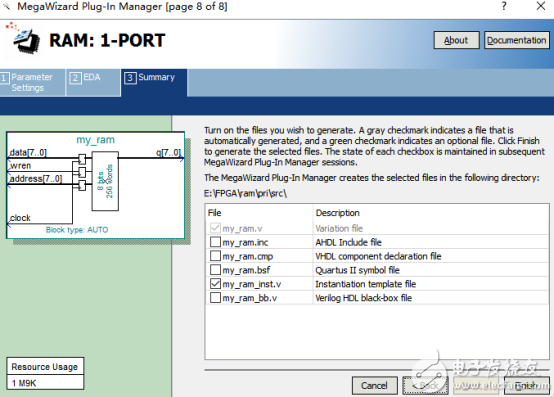

然后下一步,下一步,直接到下面的界面,选择生成.inst文件,然后完成。

设计架构图:

设计代码:

顶层模块

0moduleram(clk ,rst_n ,q); //输入输出端口设置

1 inputclk;

2 inputrst_n;

3

4 output[7:0]q;

5

6 wire[7:0]data;

7 wirewren;

8 wire[7:0]address;

9

10 ram_contl ram_contl( //例化我们的RAM控制器

11 .clk(clk),

12 .rst_n(rst_n),

13 .data(data),

14 .wren(wren),

15 .address(address)

16 );

17 my_ram my_ram_inst ( //例化ip核

18 .address (address),

19 .clock (clk),

20 .data (data),

21 .wren (wren ),

22 .q (q)

23 );

24endmodule

设计模块

0moduleram_contl(clk,rst_n,data,wren,address);

1 inputclk;

2 inputrst_n;

3

4 outputreg[7:0]data; //输出

5 outputregwren; //读写位

6 outputreg[7:0]address; //地址位

7

8 regstate;

9 always@(posedgeclk ornegedgerst_n)

10 if(!rst_n)

11 begin

12 data <=8'b0;

13 wren <=1'b0;

14 address <=8'b0;

15 state <=1'b0;

16 end

17 else

18 begin

19 case(state)

20 0:begin

21 wren <=1'b1; //打开写使能,写我们的数据

22 if(address <255)

23 begin

24 address <=address +1'b1;//地址加一,

25 data <=data +1'b1;//数据加一

26 end

27 else

28 begin

29 address <=1'b0; //写完后打开读

30 data <=1'b0;

31 state <=1;

32 wren <=1'b0;

33 end

34 end

35 1:begin

36 if(address <255) //读出我们的数据

37 begin

38 address <=address +1'b1;

39 end

40 else

41 begin

42 address <=1'b0;

43 state <=0;

44 end

45 end

46 default:state <=0;

47 endcase

48 end

49endmodule

测试模块

0`timescale1ns/1ps

1

2moduleram_tb();

3 regclk;

4 regrst_n;

5

6 wire[7:0]q;

7

8 initialbegin

9 clk =1'b1;

10 rst_n =1'b0;

11

12 #100.1rst_n =1'b1;

13

14 #200000.1$stop;

15

16 end

17

18 always#10clk =~clk;

19

20ramram_dut (

21 .clk(clk),

22 .rst_n(rst_n),

23 .q(q)

24 );

25

26endmodule

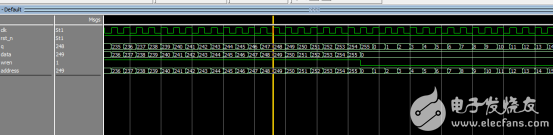

仿真图:

在图中我们可以看到,我们写入的数据,和我们读出的数据是相同的。

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有