时间:2017-12-04 17:14

人气:

作者:admin

——简化的RISC CPU设计

咱们讨论简化的RISC CPU设计。

2.RISC CPU结构

④算数运算器

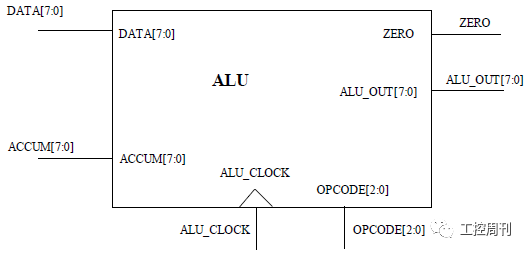

算术逻辑运算单元 根据输入的8种不同操作码分别实现相应的加、与、异或、跳转等8种基本操作运算。利用这几种基本运算可以实现很多种其它运算以及逻辑判断等操作。

其VerilogHDL 程序见下面的模块:

//------------------------------------------

module alu (alu_out, zero, data, accum, alu_clk, opcode);

output [7:0]alu_out;

output zero;

input [7:0] data, accum;

input [2:0] opcode;

input alu_clk;

reg [7:0] alu_out;

parameter HLT =3’b000,

SKZ =3’b001,

ADD =3’b010,

ANDD =3’b011,

XORR =3’b100,

LDA =3’b101,

STO =3’b110,

JMP =3’b111;

assign zero = !accum;

always @(posedgealu_clk)

begin //操作码来自指令寄存器的输出opc_iaddr<15..0>的低3位

casex (opcode)

HLT: alu_out<=accum;

SKZ: alu_out<=accum;

ADD: alu_out<=data+accum;

ANDD: alu_out<=data&accum;

XORR: alu_out<=data^accum;

LDA: alu_out<=data;

STO: alu_out<=accum;

JMP: alu_out<=accum;

default: alu_out<=8'bxxxx_xxxx;

endcase

end

endmodule

//------------------------------------------

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有