时间:2025-05-20 11:45

人气:

作者:admin

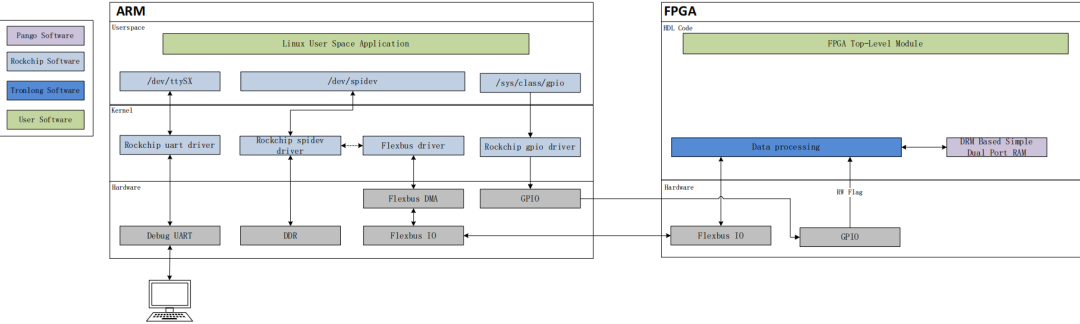

在工业领域,技术革新与突破始终是推动行业发展的核心动力。今天,为大家带来基于DSMC/FlexBus并口的RK3576J与通信方案,核心板国产化率高达100%,为工控场景带来高效、稳定的通信新体验。下面一起来看看! 开发环境与测试数据 本文主要介绍RK3576J与FPGA的通信案例,适用开发环境如下:

Windows开发环境:Windows 7 64bit、 64bit

开发环境:VMware16.2.5、Ubuntu22.04.5 64bit

U-Boot:U-Boot-2017.09

Kernel:Linux-6.1.115

Buildroot文件系统版本:Buildroot-2024.02

LinuxK:LinuxSDK-[版本号](基于rk3576_linux6.1_release_v1.1.0)

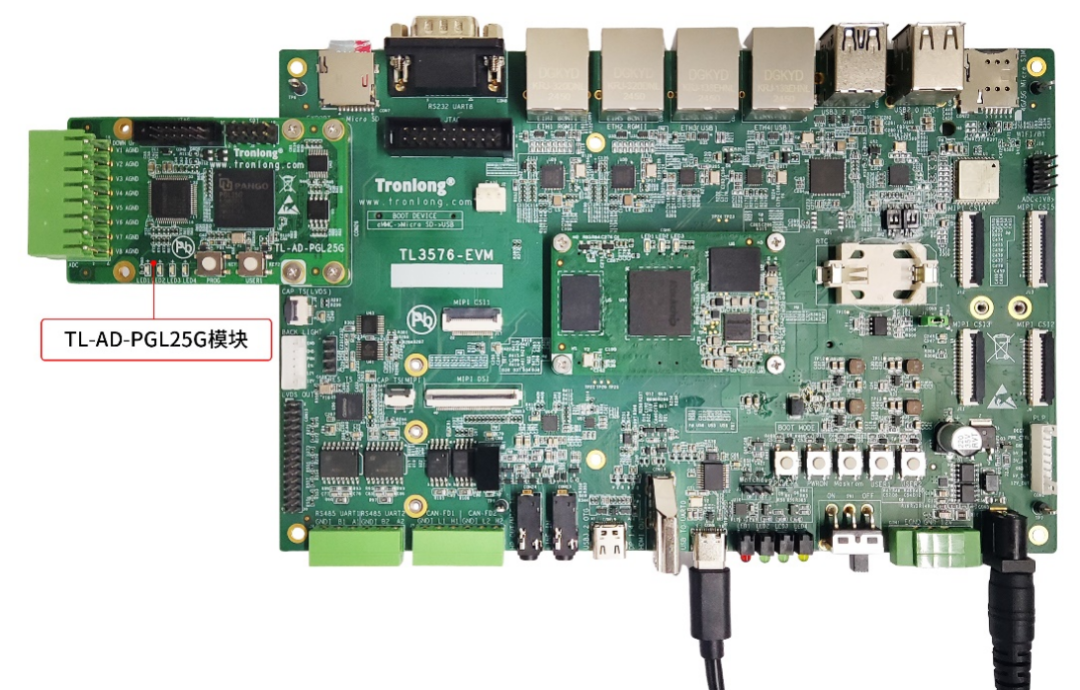

硬件平台:TL3576-EVM工业评估板(基于RK3576J)

为了简化描述,本文仅摘录部分方案功能描述与测试结果,详细产品资料请扫描文末二维码下载。 通过实测我们发现,基于DSMC和FlexBus的通信方案具备了出色性能,数据如下表所示:

| 案例 | 理论速率 | 测试结果 |

| 基于DSMC的与FPGA通信案例(dsmc_localbus__rw) |

读速率:400MB/s 写速率:400MB/s |

读速率:216MB/s 写速率:280MB/s |

| 基于FlexBus的ARM与FPGA通信案例(flexbus_rw) |

读速率:200MB/s 写速率:200MB/s |

读速率:166MB/s 写速率:165MB/s |

FPGA数采模块简介

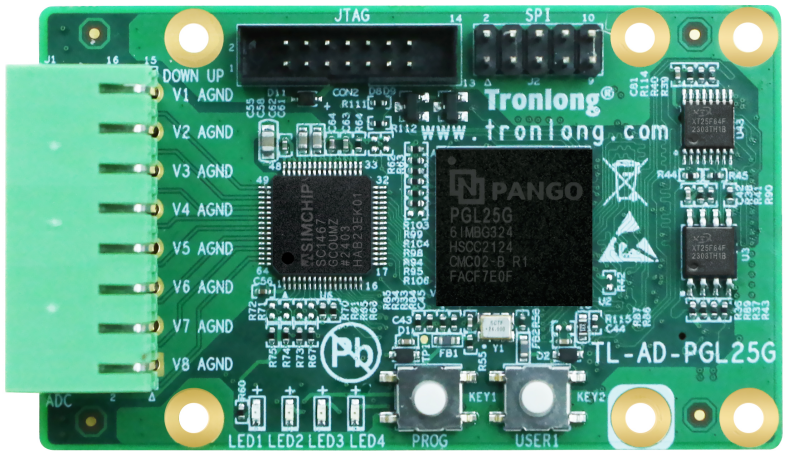

创龙TL--PGL2是一款基于紫光同创Logos PGL25G FPGA与芯炽科技SC1467/核芯互联CL1606/ AD7606 设计的数据采集模块,支持8通道、200KSPS串行/并行采样,可与ARM端通过DSMC、FlexBus、Local Bus、SPI等总线进行通信,满足客户多样化数据采集需求。

TL-AD-PGL25G模块正面图

DSMC与FlexBus并口简介 专为工业应用设计,DSMC(Double Data Ra Serial Memory Controller)作为高速并行总线,兼容多种传输协议,包括HyperBus PS、Xccela PSRAM和Local Bus。对于RK3576J,DSMC接口若使用Local Bus协议,从设备需使用瑞芯微开发的slave模型,或者传输协议相同。DSMC接口支持8/16bit串行传输模式,速率高达100MHz,可实现FPGA低成本连接,具有低延迟、高带宽和灵活配置的特点,广泛应用于需要高速通信的领域。 FlexBus是一个高度灵活的并行总线接口,可模拟标准或不规则的协议,能够适应各种复杂的通信场景。对于RK3576J处理器,FlexBus支持2/4/8/16bit并行传输,时钟速率高达100MHz,可实现高速AD/DA拓展,可以在保障数据稳定性的同时实现高效、低延迟的数据交互。这一特性使其在高速数据采集场景中具有显著优势。

RK3576J典型应用场景

高端工业

运动

工业计算机

电力监测装置

4K医疗内窥镜

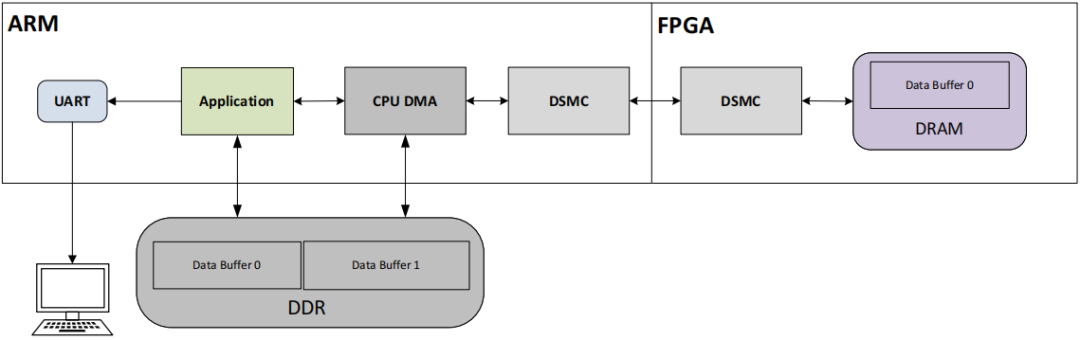

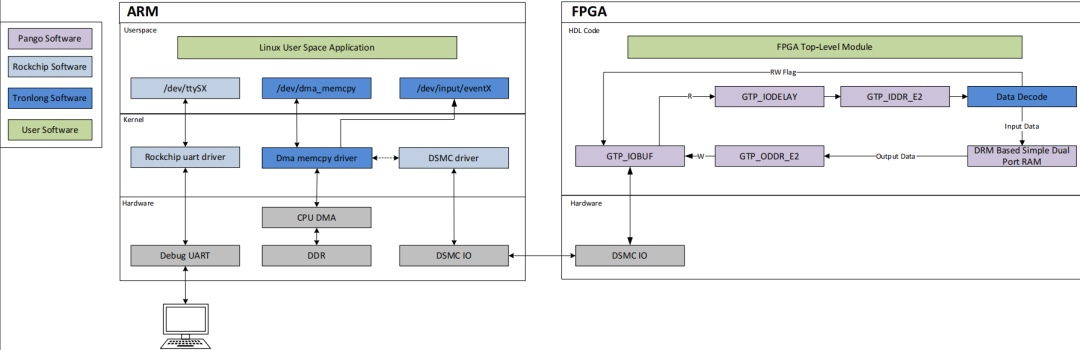

基于DSMC的ARM与FPGA通信案例

案例说明

ARM端运行Linux系统,基于DSMC总线对FPGA 进行读写测试。 程序原理说明如下:

ARM端:

ARM端使用 DMA通过DSMC总线(作为Local Bus Master)来对FPGA DRAM进行读写测试。

通过参数设置数据包大小(数据包数据每次循环均为新的随机数)、数据传输的循环次数。

对读写的数据进行校验,并打印误码率和读写速率。

FPGA端:

实现Local Bus Slave功能。

将Local Bus Master(ARM)发送的64KByte数据保存到DRAM。

当Local Bus Master(ARM)读取64KByte数据时,FPGA从DRAM读取64KByte数据发送至Local Bus。

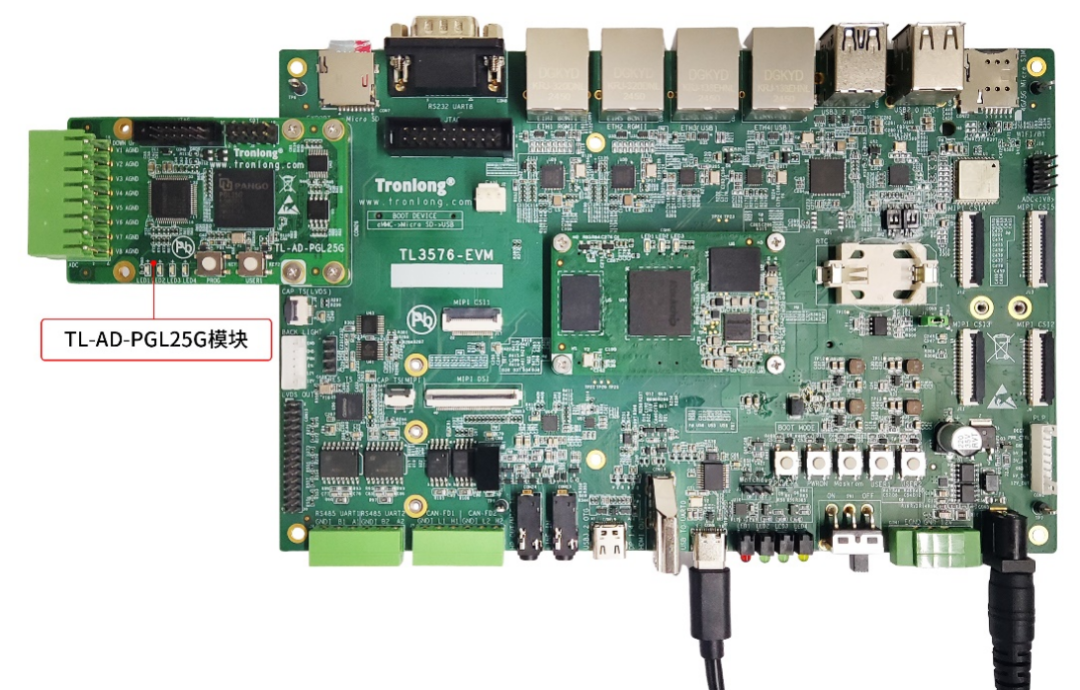

案例演示 请将创龙科技TL-AD-PGL25G模块连接至评估板EXPORT接口,如下图所示。

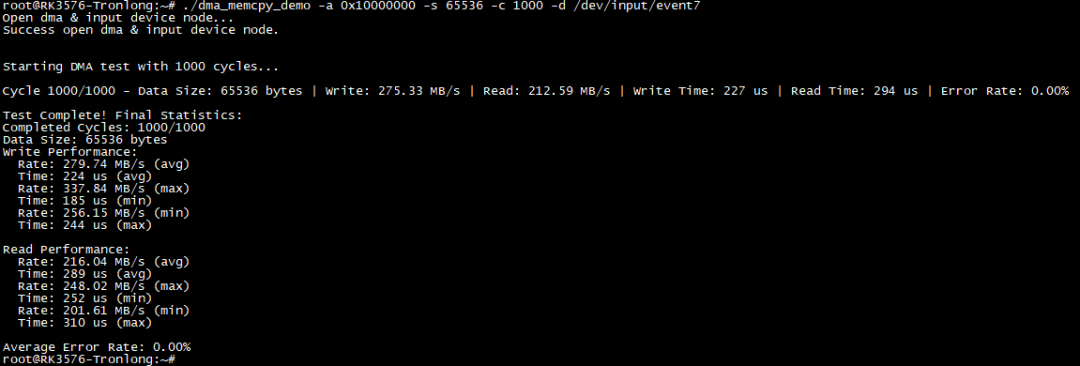

TL-AD-PGL25G模块连接图 请参考产品资料用户手册完成内核镜像替换,将FPGA可执行程序固化至SPI FLASH,并加载驱动。 执行如下命令运行程序,ARM通过DSMC总线写入65536Byte随机数据至FPGA DRAM,然后读出数据、进行数据校验,同时打印DSMC总线读写速率和误码率,如下图所示。 Target#./dma_memcpy_demo -a 0x10000000 -s 65536 -c 1000 -d /dev/input/event7

从上图可知,本次实测平均写速率约为280MB/s,平均读速率约为216MB/s,误码率为0.00%。

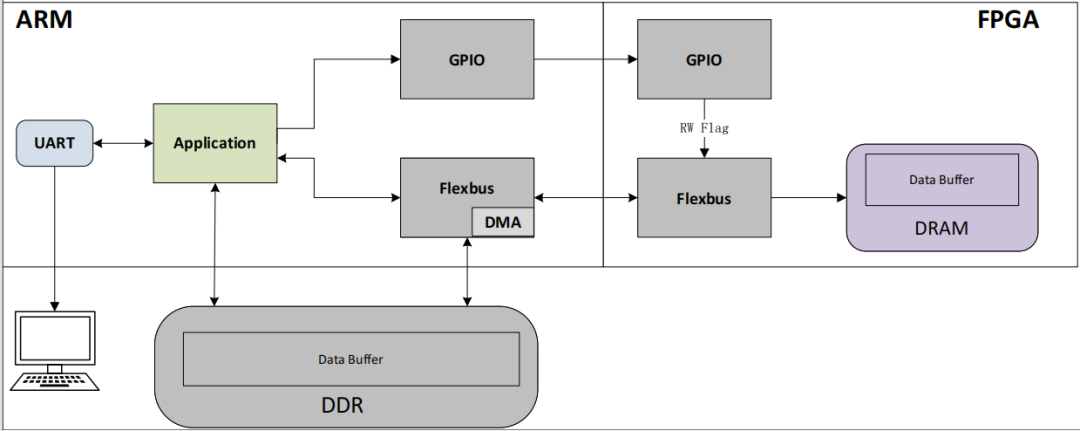

基于FlexBus的ARM与FPGA通信案例 案例说明 案例功能:ARM端运行Linux系统,基于FlexBus总线对FPGA DRAM进行读写测试。 程序原理说明如下: ARM端:

通过FlexBus总线对FPGA DRAM进行读写测试。

支持通过参数设置数据包大小(每次循环数据包的数据均为新的随机数)、数据传输的循环次数。

对读写的数据进行校验,并打印误码率和读写速率。

FPGA端:

实现FlexBus Slave功能。

默认将FlexBus Master(ARM)发送的64KByte数据保存到FPGA DRAM。

FlexBus Master(ARM)读取64KByte数据时,FPGA从DRAM读取64KByte数据通过FlexBus传输给FlexBus Master(ARM)。

案例演示 请将创龙科技TL-AD-PGL25G模块连接至评估板EXPORT接口,如下图所示。

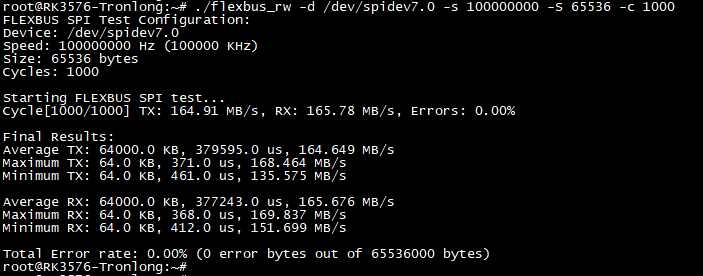

TL-AD-PGL25G模块连接图 请参考产品资料用户手册完成内核镜像替换,并将FPGA可执行程序固化至SPI FLASH。 执行如下命令运行程序,ARM通过FlexBus总线写入65536Byte随机数据至FPGA DRAM,然后读出数据、进行数据校验,同时打印FlexBus总线读写速率和误码率,如下图所示。 Target#./flexbus_rw -d /dev/spidev7.0 -s 100000000 -S 65536 -c 1000

从上图可知,本次实测平均写速率约为165MB/s,平均读速率约为166MB/s,误码率为0.00%。

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有