时间:2025-06-12 11:14

人气:

作者:admin

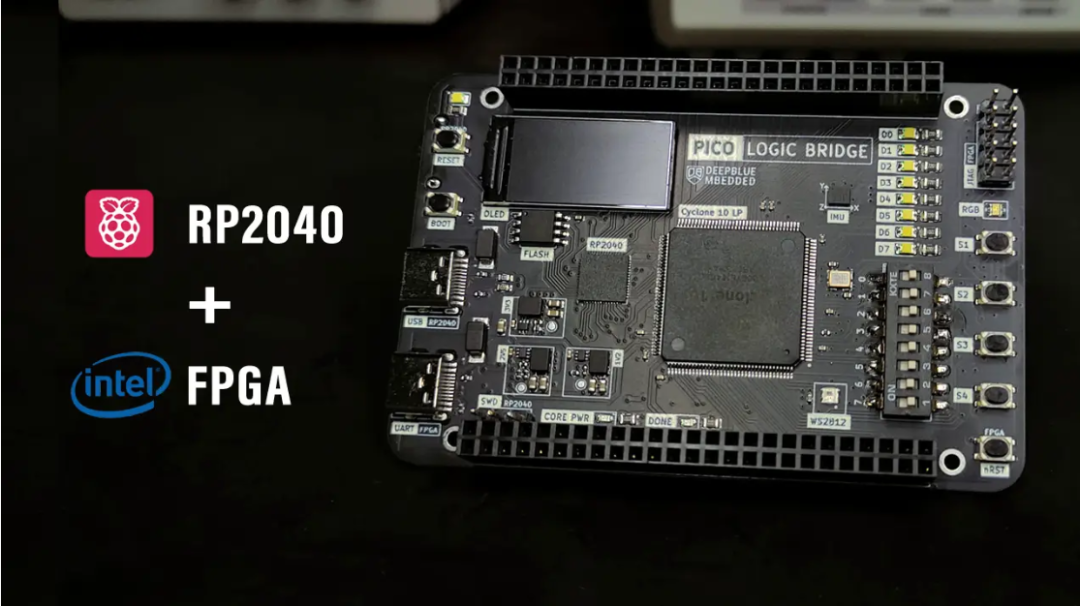

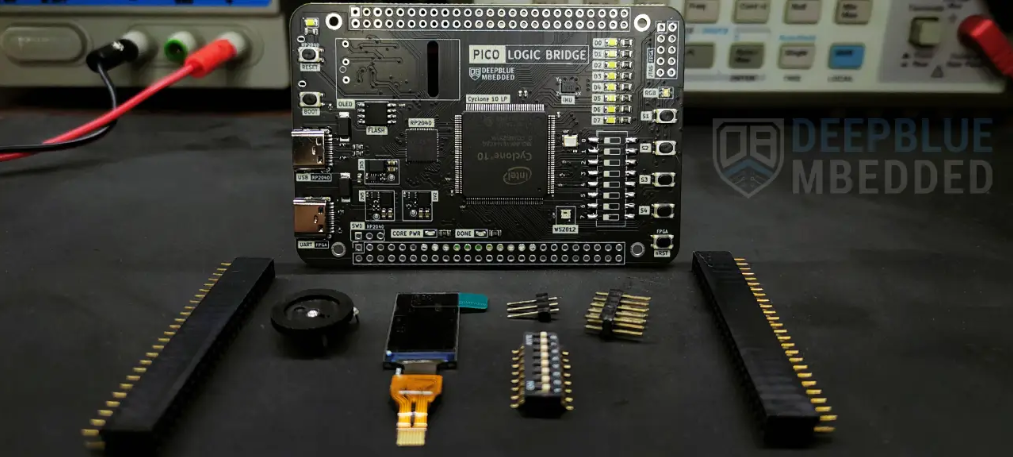

“在本文中,我将向大家展示一个结合了co (RP2040) 与 Cyclone 10 的项目。我将解释项目中的一些设计决策,如何准备生产所需的文件,以及如何在本次项目的赞助商Next完成PCBA下单。此外,我们还将用 C 语言和 硬件描述语言(HDL)开发一些固件,来共同“点亮”这块板子,并玩转它的两个核心:RP2040 和 FPGA。话不多说,让我们开始吧!”

目录

顶层硬件/软件架构

首先,这个项目背后的初衷是设计一块集成 RP2040 和低成本 FPGA 的板卡,用于实验各种芯片间的数字通信方案,例如 SPI 总线和自定义 IO 总线(使用PIO)。

我们可以将系统设置成这样:从 RP2040 的角度看,FPGA 是完全“透明”的,就像一个内存映射 I/O(MMIO)的外设扩展。反之,我们也可以在 FPGA 上实现一个软核,并将RP2040配置为一个从设备。这种架构非常灵活,拥有无限的应用可能。

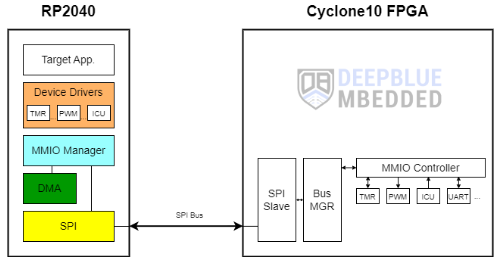

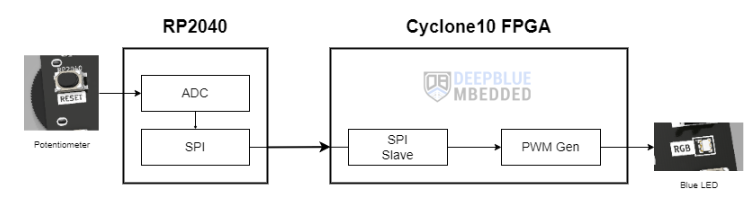

下图展示了我们项目中要实现的目标硬件/软件系统架构。

在 RP2040 这边,我们会使用一个主 SPI 外设来处理与 FPGA 的底层通信。在固件(软件栈)中,我们会实现某种形式的 MMIO 寻址、IO 读写操作、解码等。通过这种方式,我们可以将 MMIO 外设的寻址操作从固件的应用层中抽象出来。

然后,我们可以为 FPGA 上实现的自定义硬件外设编写一些固件驱动程序。这样做同样能将自定义外设的操作细节从应用层的视角中抽象出来。

最终,使用 RP2040 微控制器自身的硬件外设,和使用一个在 FPGA 上自定义设计的硬件定时器外设,体验将几乎没有差别。当然,我们不会仅仅为了多几个定时器就大费周章,但你应该能明白这个思路。

在 FPGA 这边,我们将实现一个硬件从 SPI 外设来处理与 RP2040 的通信。然后,我们会将接收到的数据传递给一个自定义的总线管理器,该管理器内部应包含某种状态机,用于编解码传入/传出的 SPI 数据。在这一步,串行的 SPI 数据将被转换为并行的总线数据/控制。

接着,我们会连接一个 MMIO ,它负责控制自定义外设的内存 IO 操作,并标准化每个自定义外设的挂载方式。这使得系统更具扩展性和可移植性。

同样,这也只是系统工作方式的一个例子。它当然也可以将 SPI 总线桥接到 AXI-4/AXI-Lite 总线,以便挂载软核处理器或标准的硬件 IP 核,可能性还有很多。

RP2040 微控制器和 Cyclone 10 FPGA 芯片之间有两条总线连接:

SPI 总线 (4线)

使用 SPI 总线,我们可以利用 RP2040 的硬件外设与 FPGA 进行高速通信(最高可达62.5Mbps)。我们还可以通过 RP2040 内部的 单元实现批量数据传输,从而极大地减少 的干预。

自定义IO总线 (4线)

利用 RP2040 独特的 PIO(可编程I/O),我们可以轻松实现任何自定义的数字通信协议,以达到非常高的数据传输速度。这为未来的无限可能性和实验敞开了大门。

在设计这样的系统时,官方文档和指南是我们最好的朋友。/提供了许多非常有用的文档,我在设计这块板子时都用到了,包括:

RP2040 也是如此,树莓派官网上有几份很有帮助的文档:

你也可以参考我之前关于 RP2040 的项目,它演示了如何围绕 RP2040 微控制器设计自定义 PCB 板,我在这个项目中也完全沿用了那部分设计。

https://deepbluembedded.com/raspberry-pi-pico-rp2040-schematic-pcb-design-in-/

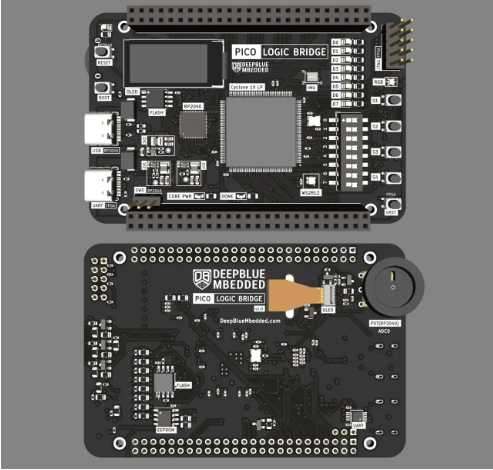

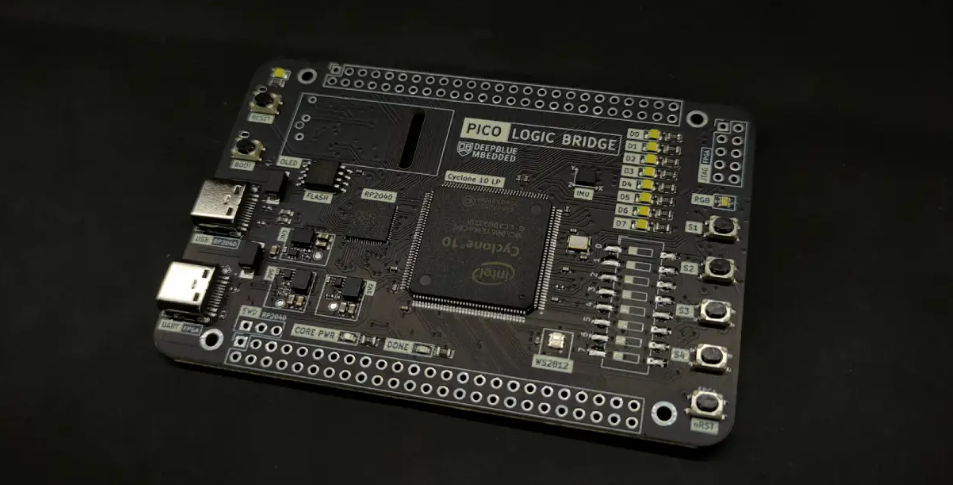

这是板子在KiCAD 3D视图中的顶层和底层布局。我特意将所有东西按逻辑分区,并保持其易用性。在 CAD 软件里看起来很大的 PCB,现实中很容易变得笨拙难用。我尽力将用户需要交互的元件放在易于触及和操作的位置。

板子尺寸为:6cm x 9cm(它非常小,不像在CAD软件里看起来那么大)

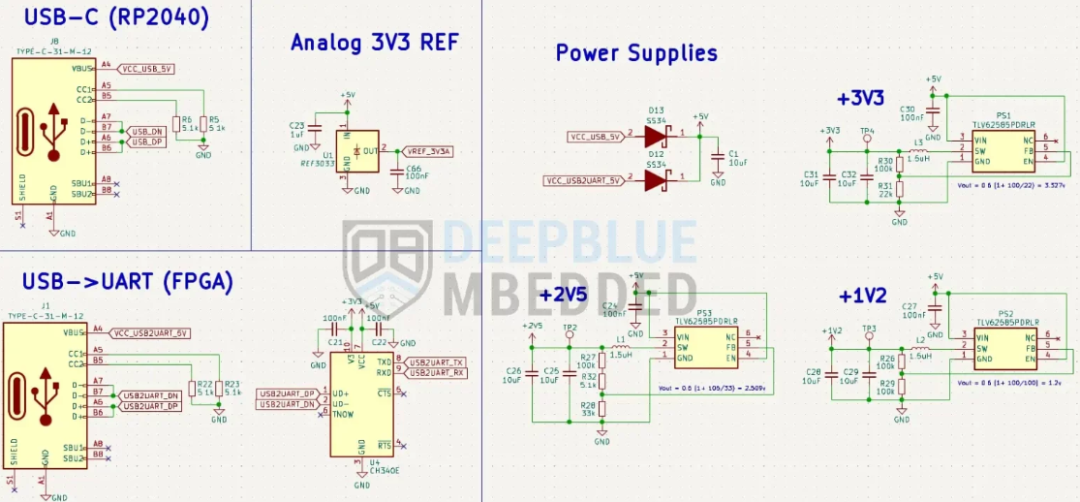

1. 直流输入 +

板上有两个 USB-C ,一个用于电源输入(+5V)和 RP2040 的 USB 通信(UF2烧录程序时需要),另一个 USB 口连接到一个 USB 转 桥接芯片,通往FPGA。

2. 电源 (稳压器)

板上有三个 和一个电压参考,它们分别是:

3. RP2040 电路 + QSPI FLASH

RP2040 微控制器需要 +3.3V 的 IOVdd 输入电压、内部稳压器提供的 +1.1V 核心电压、100nF 的去耦电容和一个 12MHz 的晶体。

与市面上大多数微控制器不同,RP2040 没有内置闪存,因此需要一个外部 QSPI 闪存芯片。你可以选择2MB、4MB、8MB或16MB的闪存。

在我的板子上,我使用了 RP2040 的 XIP(eXcu-In-Ple)接口所允许的最大闪存容量:16MB(128Mbit)。

我还增加了一个RESET按钮,以及用于UF2编程的BOOT按钮。

4. Cyclone 10 LP (10CL006) FPGA电路

FPGA 芯片有很多 Bank 和特殊功能的 IO 引脚,需要按照 Intel/Altera 官方文档中详细说明的方式进行连接。

VCCIO、VCCA 和 VCCINT 引脚都按数据手册建议连接。MSEL[2:0] =ASx1(Active Serial) 模式允许 FPGA 从一个 SPI 串行闪存芯片加载配置比特流。我使用了一个64Mbit的QSPI闪存芯片。

我用作 FPGA 主时钟源的 CMOS 振荡器是一个50MHz的振荡器。当然,我们可以利用 FPGA 内部的2个PLL单元来调整这个频率(这款FPGA的PLL最高可达400MHz)。

5. RP2040 板载外设

连接到RP2040微控制器的板载外设有:

6. FPGA 板载外设

连接到Cyclone 10 LP FPGA的板载外设有:

7. IO

板上有4组端口:

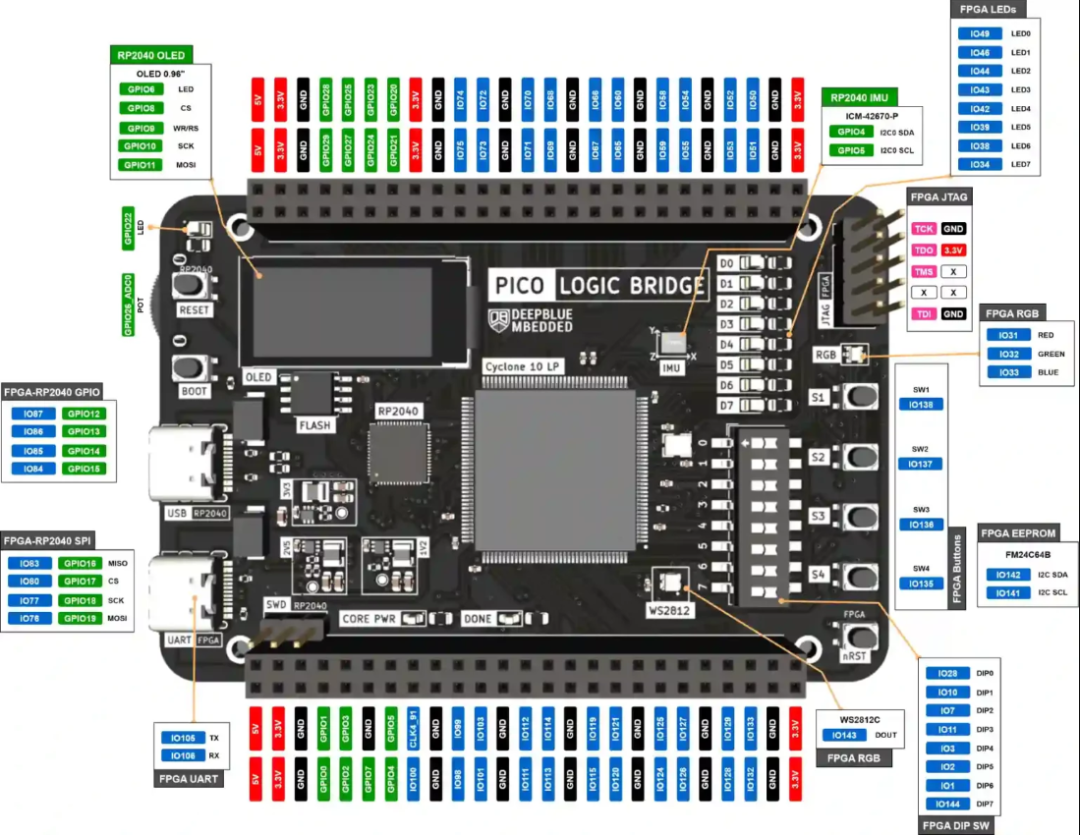

RP2040+FPGA 板引脚定义图

这是我们项目板卡的引脚定义图。

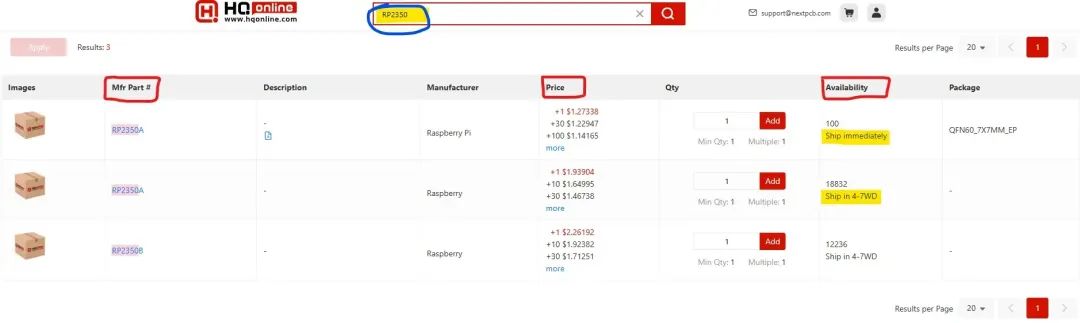

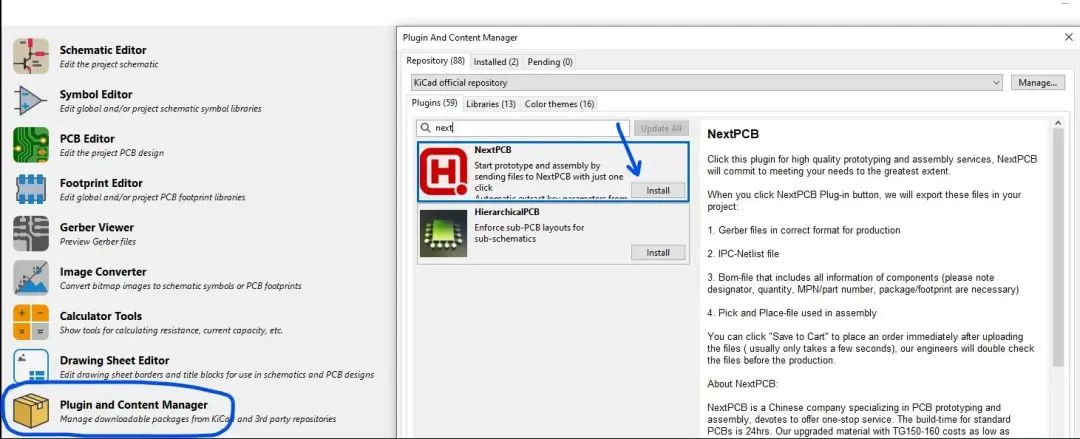

在 @NextPCB 上下单

可以在网页上下单,也可以使用 KiCad 的插件:

到货了!

首先,我需要手动焊接/安装一些直插。

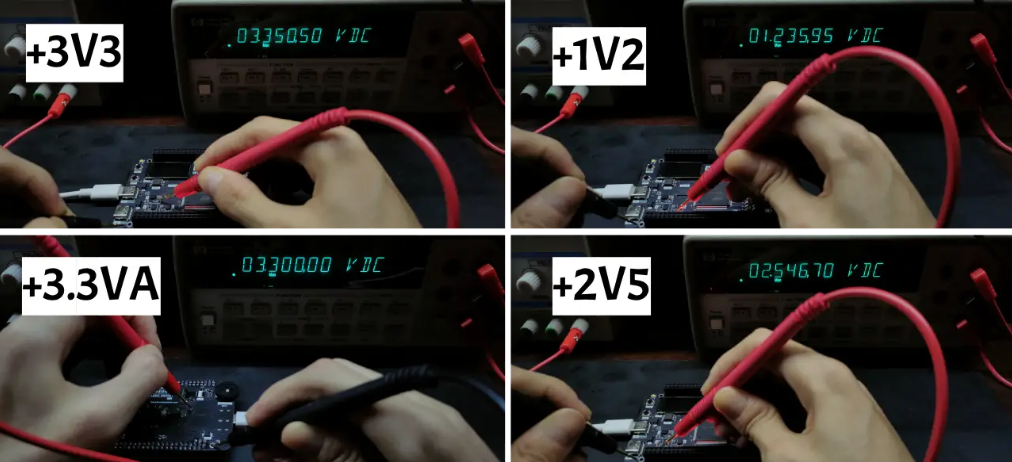

然后,我用显微镜和“Fine Needle”探头快速检查,确保关键电源网络没有短路,并检查关键电源路径(VCC, VCCINT, VCCA等)的导通性。

一切看起来都很完美。下一步,我从我的“限流”电源上给板子通电(+5V/50mA)。这样做是为了以防万一,即使有问题,也不会有足够大的造成严重损坏。谢天谢地,它完美地工作了起来,只消耗了几个毫安的电流。

以下是实际测量的电源电压:

到这一步,我信心十足地插上了 USB 线,准备开始真正的测试工作!

这是第一个“RP2040测试”示例,我们将闪烁板载的 LED 灯。编译固件并使用 UF2 引导加载程序将其烧录到板子上。

测试结果:LED成功闪烁!

接下来,我们测试 RP2040 的 ADC。通过读取板载的模拟旋转电位器的值,然后用它作为占空比控制信号,来调节板载 LED 的亮度。

测试结果:转动电位器,LED亮度平滑变化。

这是第一个“FPGA测试”示例。我将 8 个 DIP 开关通过 FPGA 内部连接到 8 个 LED,用灯的状态。同时,将 3 个按键连接到 RGB LED 的红、绿、蓝引脚。这是一个非常基础的测试,用来验证 FPGA 至少能正常工作,并能接收比特流文件来执行相应的功能。

测试结果:开关和按键都能正确控制对应的LED。

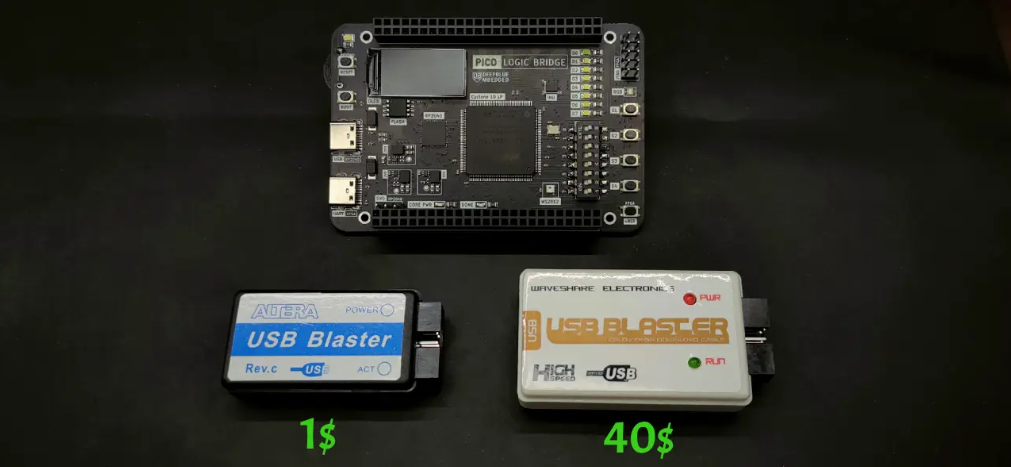

为了将比特流加载到我的 Cyclone 10 FPGA 上,我尝试了市面上常见的两种 Altera USB Blaster。由于我使用的是最新版本的 Prime(精简版),所以 Waveshare USB Blaster v2 对我来说比较好用。

不过,便宜的 USB Blaster 也能用,也能检测到,驱动程序也能安装,一切正常。但它在我这里没有出现在 Quartus Prime 软件中。也许它在旧版本的软件包下能用。

在之前的示例中,只要按下复位按钮或断电,FPGA的 配置(比特流)就会丢失。因此,我们需要测试 QSPI Flash 的配置功能。我将比特流准备成JIC(JTAG间接配置)文件格式,然后通过JTAG连接将其烧录到QSPI存储器中。

这将使我们的FPGA设计永久存储在QSPI闪存中,并在上电或按下复位按钮后自动加载。

测试结果:断电重启后,FPGA 成功加载了之前的配置,功能恢复正常。

现在,我们来进行真正的核心测试。在这个例子中,我们将实现:

因此,RP2040的电位器将控制 FPGA 的 PWM 输出,进而控制 RGB 上蓝色 LED 的亮度。我们将 SPI 通信速度设置为1Mbps以确保一切正常,然后再逐步提高速度。

测试结果:完美实现!转动电位器,蓝色LED的亮度随之变化。

在对系统在 1Mbps SPI 速度下的性能充满信心后,我开始逐渐提高 SPI 通信速度。当速率达到 30Mbps 时,通信开始出错,这是因为我的 FPGA 使用的是板载的原始 50MHz 源。

因此,我启用了 FPGA 内部的一个PLL单元,将时钟“泵”到 30Mbps,并将该时钟提供给我所有的HDL模块(尤其是SPI从机)。这样做之后,我们就可以在62.5Mbps 的速率下轻松维持稳定的 SPI 通信,这也是 RP2040 在 125MHz 系统时钟下运行时的最高 SPI 速度。

这对我来说简直太棒了!因为我在网上看到很多关于 SPI 线路端接以及在速度超过 30MHz 时会出现问题的讨论。而我没有使用任何并行或串联端接电阻,只是遵循了信号完整性的通用布线最佳实践。

在结束本项目之前,最后一个示例演示是板载 0.96 英寸 OLED RGB 显示屏。以下是一段演示,展示了一些存储在 RP2040 上并在 OLED 屏幕上显示的图像。

鉴于这是该硬件设计 PCB 项目的首次迭代。目前,所有测试都按预期运行,没有任何问题。这已经是一个很大的成功了!

如果其他辅助外设也能正常工作,那将是额外的胜利。剩余未测试的外设包括:

IMU (ICM-42670) – [RP2040]

I2C EEPROM (24C64) – [FPGA]

Neopixel RGB (WS2812) LED – [FPGA]

我没有时间为上述部件开发一些设备驱动程序,但我相信它们也能正常工作。

通过这个项目,我希望你觉得它对你有帮助、有启发,或者至少觉得它很有趣。我有很多想用这块板子做的实验,特别是微控制器和 FPGA 之间的数字通信。我将尽力记录后续的工作,并希望能在我们的油管频道上分享一些内容,敬请关注。

如果你有任何问题,或者希望我用这块板子做一个特定的应用,甚至是用不同的规格(FPGA、MCU、传感器、外设等)创造一块新板子,欢迎在评论中告诉我。我很乐意听听你的看法。

以下是油管的完整项目视频链接:

https://youtu.be/bl_8qcS0tug

本文转载自:https://deepbluembedded.com/rp2040-cyclone-10-fpga-pcb-design-project/,经过翻译、校对

下一篇:FPGA与高速ADC接口简介

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有