时间:2025-06-12 14:18

人气:

作者:admin

引言:本文介绍与高速方式和标准以及J204与FPGA高速串行接口。

1. 高速C与互联需要权衡的因素

如图1所示,ADC可以与、、FPGA以及均可以实现互联,在进行选择时,需要考虑以下因素:设计要求的处理和性能、开发成本、IO接口速率、开发的便利性以及器件材料成本。

图1:ADC与处理器互联需要权衡的因素

2. 高速ADC常见的接口形式

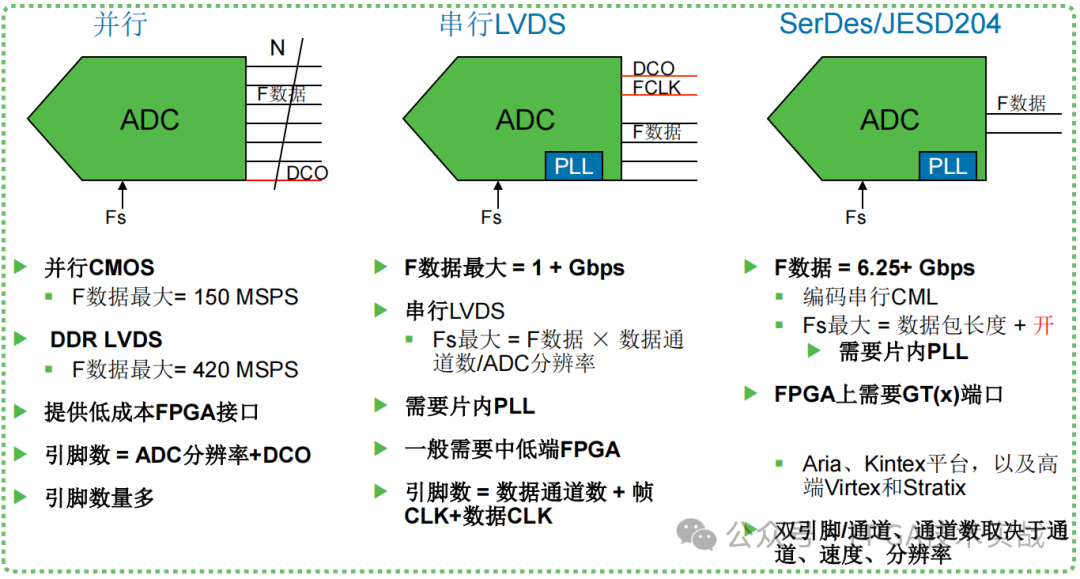

(1)并行接口

并行接口又可分为并行CMOS和并行 LVDS接口。CMOS并行接口一般速率在150MSPS,DDR LVDS ADC可达420MSPS速率,通常对FPGA接口性能要求不高,在低档FPGA接口实现,但是由于采用并行接口,这种ADC占用的FPGA IO管脚数量较多。

(2)串行LVDS接口

串行LVDS ADC最大速率可≥1Gbps,通常ADC片内集成倍频PLL,由于数据数量较高,通常需要中端FPGA实现互联,与FPGA互联的引脚数与使用的数据通道数有关。

(3)JESD204B接口

JESD204B ADC最大数据速率≥6.2bps,通常常用串行CML接口标准。需要使用FPGA接口才可互联,一般需要中高端FPGA,由于采用Gbps收发器,使用的FPGA IO引脚数较少。

高速ADC常见的接口形式对比如图2所示。

图2:高速ADC常见的接口形式对比

3. 高速ADC常见控制接口

高速ADC的控制接口几乎都独立于数据接口,通常为SPI,有时为或引脚可(物理管脚配置)。控制接口通常用于访问转换器的,实现芯片控制。

控制接口运行速率比数据接口慢得多,SPI运行速率通常小于40 MHz (5 Mbps)。

4. JESD204串行接口

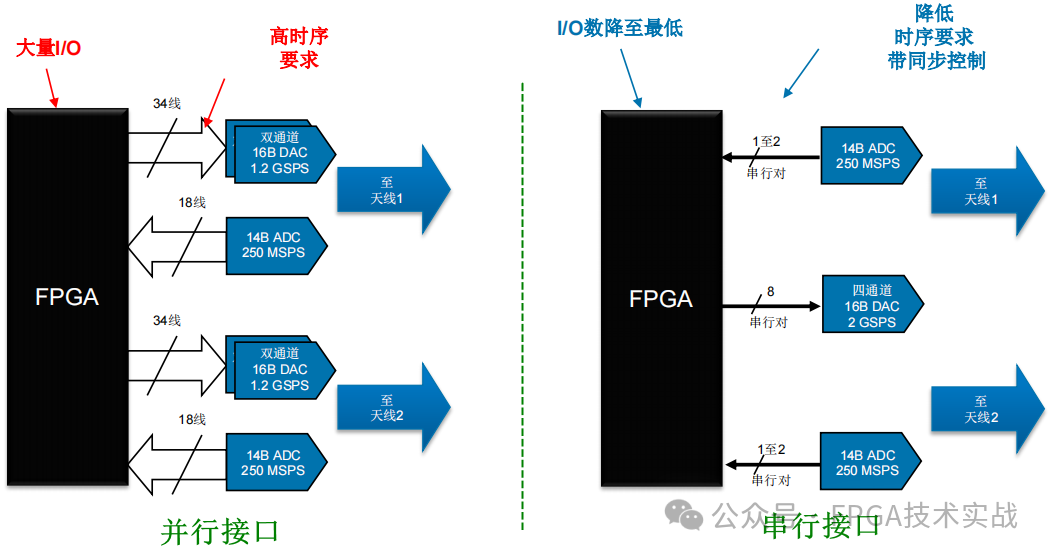

(1)采用JESD204串行接口优点

如图3所示,采用JESD204串行接口优点较多。

图3:并行接口与串行接口对比

1)简化整体系统设计

减少走线路径,简化电路板走线设计;

简化同步时序设计。

2)引脚数减少 – Tx和Rx均是如此

引脚数量多的低速并行接口转为引脚数量少的高速串行接口;

集成进一步减少引脚数。

3)降低系统成本

更小的IC封装和电路板设计可降低成本。

4)轻松扩展满足未来带宽需要

几何尺寸更小、速度更快,更好地适应标准。

(2)JESD204标准演进

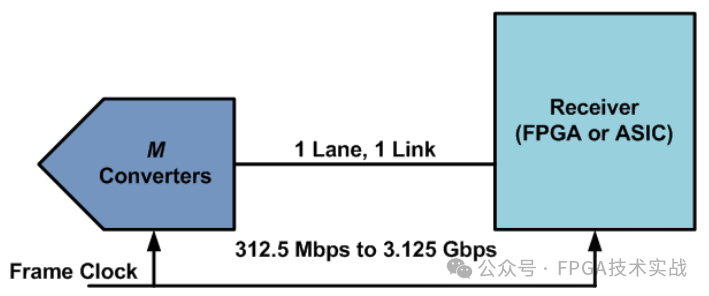

JESD204,是JEDEC定义的针对高速点对点串行接口的一项标准,用于互连两个(或更多)器件,如转换器到数字、数字源到或数字源到数字接收器。

与以前的转换器接口相比单个主机串行接口可用来传递所有数据、时钟和帧信息。时钟和帧信息嵌入数据流中,无需担心数据和时钟之间的设置建立和保持时间。

图4:JESD204标准链路

JESD204这种标准在转换器和接收器(通常为FPGA或ASIC)定义了一种数千兆位的数据链路。

如图4所示,JESD204(2006年4月)原有标准只定义了一条通道、一条链路对采样通过单个串行通道到多个转换器的传输进行了定义,最高速率为3.125Gbps。

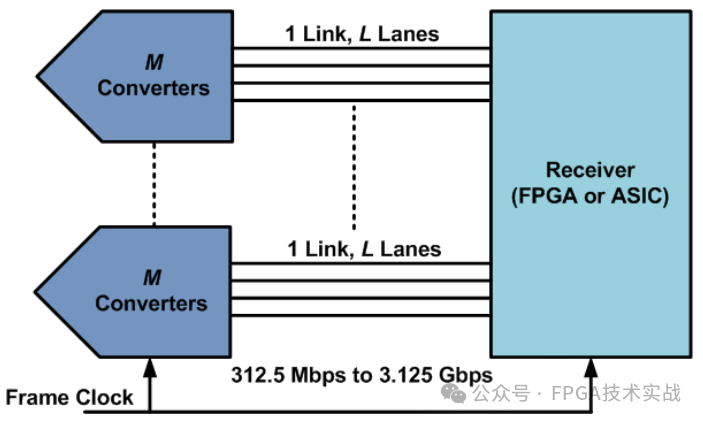

图5:JESD204A标准链路

如图5所示,JESD204A(2008年4月)—首次修订,将原有标准扩展成多条链路和多个通道。修订版增加了通过多个对齐串行通道向多个转换器传输数据的能力,最高速率为3.125 Gbps。

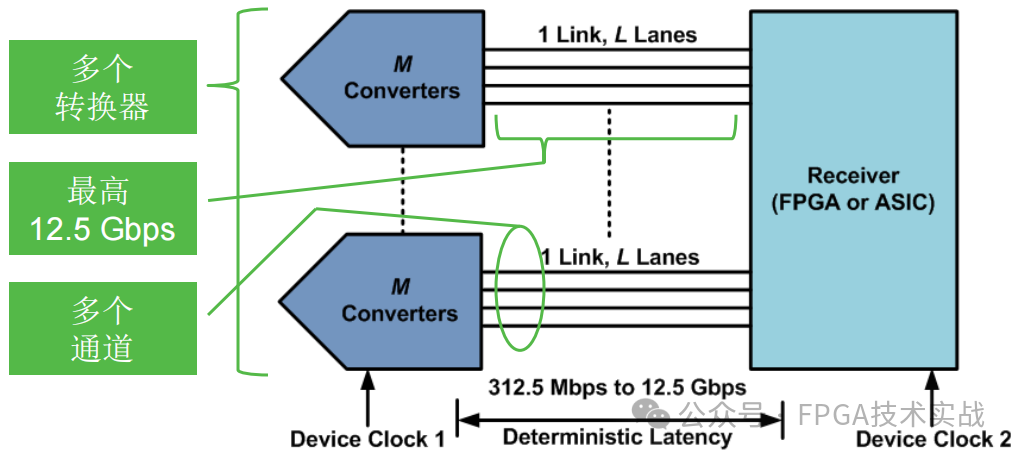

图6:JESD204B标准链路

如图6所示,JESD204B(2011年8月),第三版,运用一个器件时钟,同时增加了多项措施以确保获得确定性的延迟。支持通过多个对齐的串行通道向多个转换器传输数据,最高速率为12.5Gbps。

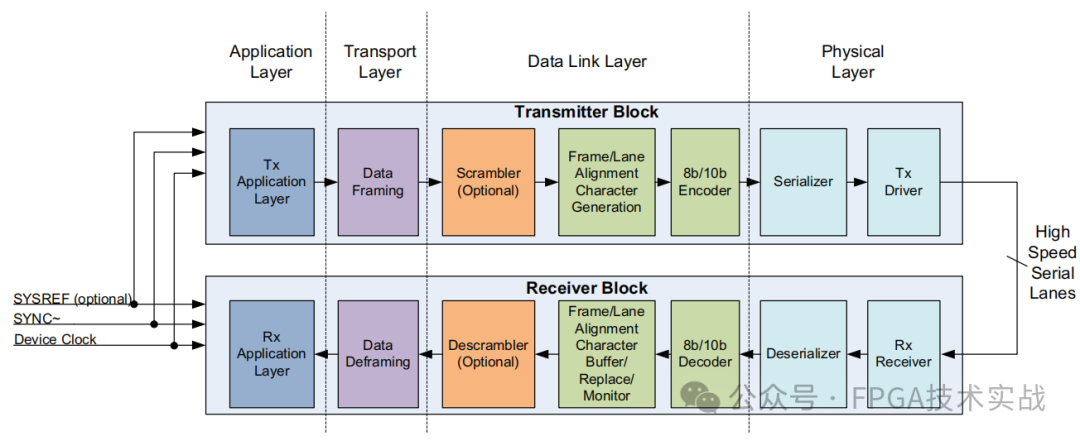

(3)JESD204标准各层

图7:JESD204B各层的简化数据流

如图7所示,JESD204B标准是一种分层规范,规范中的各层都有自己的功能要完成。应用层支持JESD204B链路的配置和数据映射。传输层实现转换样本与成帧未加扰八位字之间的映射。加扰层可以选择性地获取八位字并进行加扰或解扰,以便通过延展频谱尖峰来降低EMI效应。加扰在发送器中完成,解扰在接收器中完成。在数据链路层中,可选加扰的八位字编码成10位字符。该层也是产生或检测控制字符的地方,目的是监视和维护通道对齐。物理层即串行器/解串器(SERDES)层,负责以线路速率发送或接收字符。该层包括串行器、、接收器、时钟和数据恢复电路。

(4)JESD204B 标准中关键信号

1)器件时钟(Device clock)

系统中的一个时钟信号,为链路中数据的帧速率的谐波;

在JESD204B系统中,帧时钟不再是主机系统参考源。

2)SYNC~

从接收器到发送器的一个系统同步低电平有效信号,表示同步状态;

当SYNC~为低电平时,接收器和发送器同步;

如果涉及多个DAC/ADC,则可将SYNC~组合起来。

3)通道0、 … 、 L-1

链路中的差分通道(通常为高速CML);

8B/10B代码组按先MSB/后LSB方式传输。

4)SYSREF(可选)

一个可选的源同步、摆率时序分辨率信号,用于重置器件时钟分频器(包括LMFC),以确保获得确定性的延迟。

同时分配至系统中的ADC/DAC和ASIC/FPGA逻辑器件,可用时,SYSREF是JESD204B系统中的主机时序参考,因为它负责重置LMFC参考。

(5)JESD204x 标准中确定性延迟

当从JESD204x接收器输入端到JESD204x接收器输出端的时间始终为相同时钟周期时,则延迟具有确定性;

在并行实现中,确定性延迟很简单—时钟随数据传输;

在串行实现中,存在多个时钟域,结果可能造成不确定性;

JESD204和JESD204A并未针对如何确定延迟的确定性进行规定

JESD204B通过规定三个器件子类,试图解决这一问题:

器件子类0—不支持确定性延迟;

器件子类1—利用SYSREF(500 MSPS以上)实现确定性延迟;

器件子类2—利用SYNC(最高500 MSPS)实现确定性延迟。

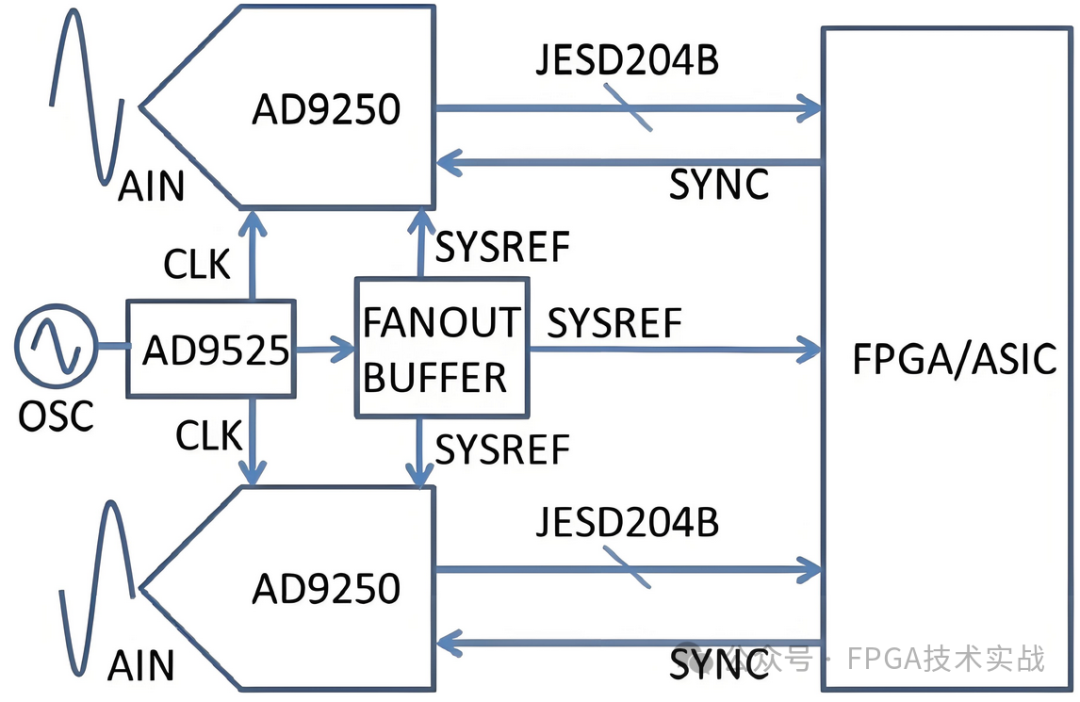

(6)JESD204B硬件应用示例

图8:JESD204B ADC与FPGA硬件连接示例

如图8所示,AD9250是来自公司的250 MSPS 14位双ADC,支持子类1实现中的JESD204B接口。该子类允许使用SYSREF事件信号跨ADC进行采样同步。AD9525是一款低抖动,不仅提供高达3.1 GHz的七个时钟输出,而且能够根据用户配置同步SYSREF输出信号。这两种产品,再加上ADI公司的一系列扇出缓冲器产品,提供了一个框架,可以精确同步和对齐发送到FPGA或ASIC进行处理的多个ADC数据。

来源:本文转载自FPGA技术实战公众号

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有