时间:2025-01-22 11:39

人气:

作者:admin

简介

TI60F100-DK是一款采用易灵思Ti60F100开发的评估板。

采用底板和核心板分离的方式来实现。单独的核心板主要是考虑有客户可能需要自己定制底板。

特性说明:

(1)单TypeC usb不仅支持供电,还同时实现JTAG下载、SOFT JTAG软核调试及UART三个功能;

(2)千兆以太网。支持裕太的YT8531SH,高效稳定。

(3)HDMI输出。LVDS实现HDMI输出,分辨支持1080p@60,HDMI支持音频输出;

(4)外扩Flash。Ti60F100片上Flash为16Mb,而外扩Flash可以根据需要任意扩展;

(5)用户LED。两个;

(6)用户按键。两个;

(7)MIPI扩展。最大支持两组MIPI x4发送,支持1组MIPI x4接收;

(8)LVDS扩展。10对差分对可用于LVDS接收或者发送;

(9)扩展IO。27个IO。

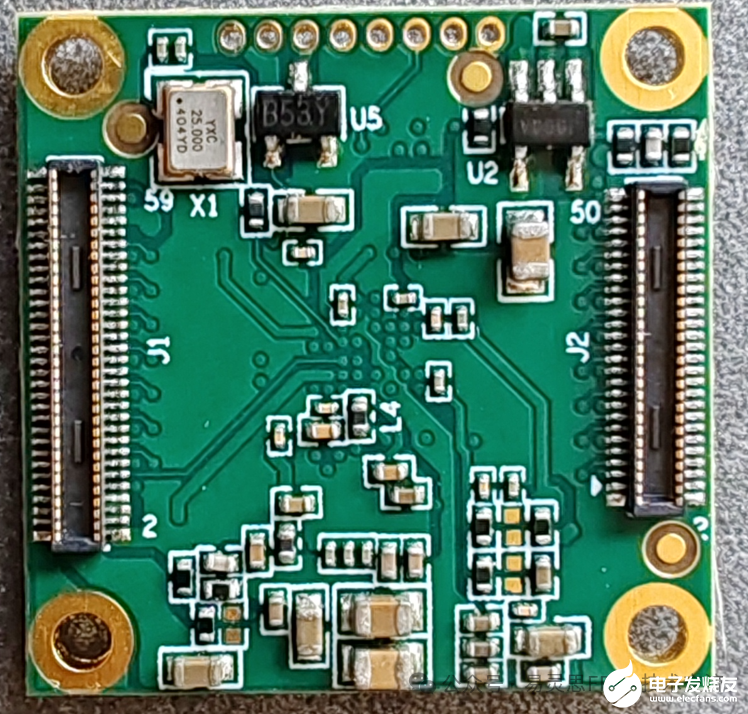

核心板

TI60F100-DK采用底板与核心板分离的结构。用户可以通过核心板外扩自己的外设实现制定功能。以下是核心板的硬件设计说明。核心板主要是把IO引出来。方便客户自己定义功能。

IO座子分别为50Pin和60Pin,可以确保防反插。Pin间距为0.4mm。

核心板尺寸为2.4cm x 2.4cm。

(1)核心板电源

核心板电源包括0.95V,1.8V和1.2V。保证核电压及IO电压供电,1.2V为MIPI Bank电压供电。客户可以根据需要配置Bank电压为1.8V或者1.2V.

(2)时钟

核心板配有一个25M的晶振

| 编号 | 时钟频率 | 管脚名 | 管脚号 | Bank电压 | Bank |

| X1 | CLK_25M | GPIOL_P_07_CLK0_P | F4 | 1.8V | 1A_4B |

表1

(3)上电时序

Ti60F100对上电时序是有要求的。Demo板按上电要求进行了配置。

(4)差分对等长处理

核心板做了三组等长的差分对,以备客户进行底板开发时有底板需求。等长为3mil,请确认三组分别等长,组与组之间没有等长关系。

| 组 | 差分对 | 用作MIPI | 用作LVDS | 说明 |

|

第 一 组 |

GPIOR_PN_00 | MIPI_DATA | PLL_RX_CLK |

MIPI_RX_CLK:说明 该差分对可以用作MIPI RX的时钟; PLL_RX_CLK:说明 该管脚可以连接 LVDS的参考时钟。 |

| GPIOR_PN_01 | MIPI_DATA | DATA | ||

| GPIOR_PN_02 | MIPI_RX_CLK | DATA | ||

| GPIOR_PN_03 | MIPI_DATA | DATA | ||

| GPIOR_PN_04 | MIPI_DATA | DATA | ||

| GPIOR_PN_05 | MIPI_DATA | DATA | ||

| GPIOR_PN_06 | MIPI_DATA | DATA | ||

| GPIOR_PN_07 | MIPI_DATA | DATA | ||

| GPIOR_PN_08 | MIPI_DATA | DATA/GCLK | ||

| GPIOR_PN_09 | MIPI_DATA | DATA/GCLK | ||

|

第 二 组 |

GPIOR_PN_10 | MIPI_RX_CLK | DATA/GCLK | |

| GPIOR_PN_11 | MIPI_DATA | DATA/GCLK | ||

| GPIOR_PN_12 | MIPI_DATA | DATA | ||

| GPIOR_PN_13 | MIPI_DATA | DATA | ||

| GPIOR_PN_14 | MIPI_DATA | DATA | ||

|

第 三 组 |

GPIOL_PN_09 | MIPI_RX_CLK | DATA/GCLK | |

| GPIOL_PN_10 | MIPI_DATA | DATA/GCLK | ||

| GPIOL_PN_11 | MIPI_DATA | DATA | ||

| GPIOL_PN_12 | MIPI_DATA | DATA | ||

| GPIOL_PN_13 | MIPI_DATA | DATA | ||

| GPIOL_PN_18 | PLL_RX_CLK |

表2

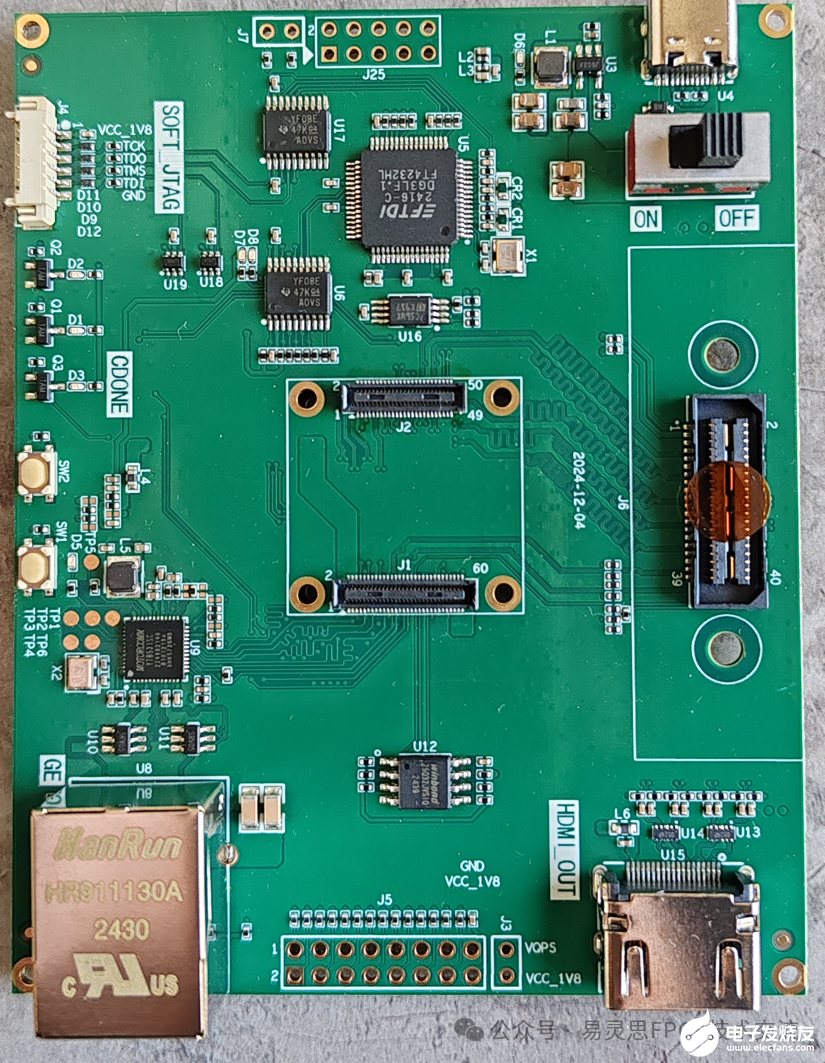

底板

目前底板主要提供了,尺寸为10x8cm

(1)电源

底板通过TypeC USB供电。使用方便简单。另外只需要一个USB线就可以同时实现JTAG下载、softJTAG软核调试及UART。所以在使用上会非常简单。

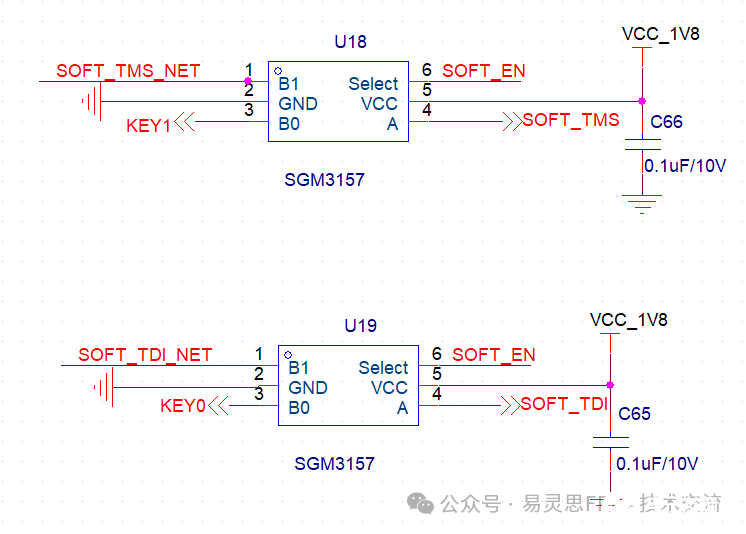

(2)用户按键

硬件图片

| 按键丝印 | 按键编号 | FPGA Name | FPGA Num | 说明 |

| SW2 | KEY0 | GPIOR_P_19_PLLIN0 | A9 | 如果使用按键需要J7 Header短接,并且按键与SOFT JTAG共用IO |

| SW1 | KEY1 | GPIOR_N_19 | A10 |

表5

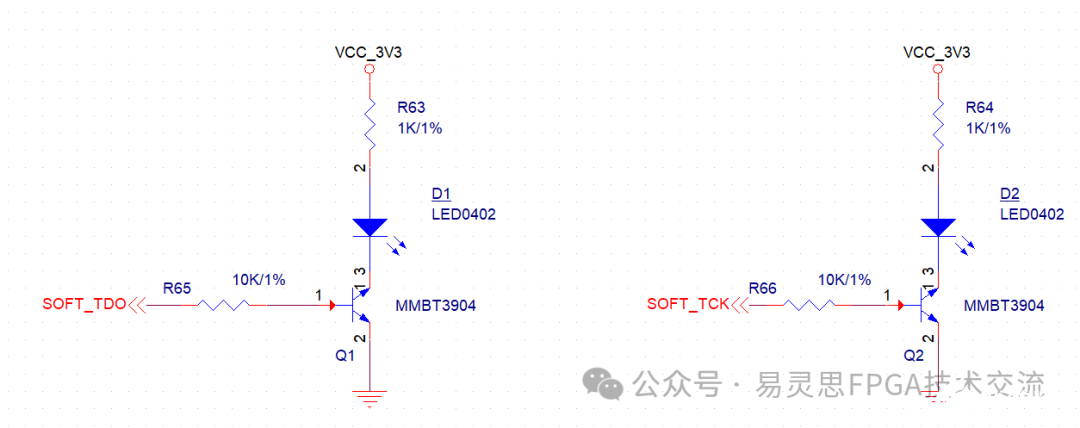

(3)用户LED

| 按键编号 | FPGA Name | FPGA Num | 说明 |

| D1 | GPIOL_P_11 | E2 | 请注意LED与SOFT JTAG共用IO |

| D2 | GPIOL_N_11 | E3 |

表6

请注意:由于Ti60F100 IO有限,所以LED,按键是和soft JTAG共用IO

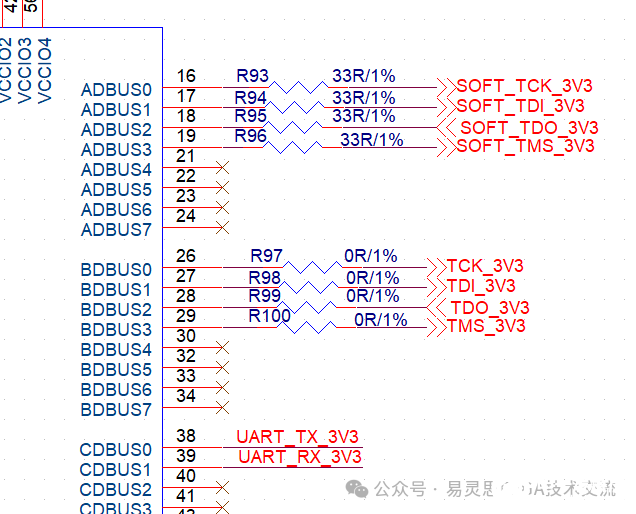

(4)板载下载器、SOFT JTAG及UART

底板配有FT4232板载程序配置方案,不需要外挂,所以连线非常简单,稳定性也更好;另外FT4232还可以同时支持UART,所以实现一线三用的功能。

Demo板使用下载芯片的第三路作为UART

| SIGNAL | FPGA Name | FPGA Num | 说明 |

| UART_RX | GPIOR_N_10_CLK9_N | C7 | UART_RX:FPGA为input;UART_TX:FPGA为output; |

| UART_TX | GPIOR_P_10_CLK9_P | D6 |

表7

易灵思的soc与逻辑不能共用JTAG同时调试,所以需要通过IO模拟JTAG,该demo板,下载芯片可以同时实现JTAG下载及SOFT JTAG高度功能。

| SIGNAL | FPGA Name | FPGA Num | 说明 |

| SOFT_TMS | GPIOR_P_19_PLLIN0 | A9 | 对于FPGA来说,SOFT_TDO为output,其余为input。使用softJTAG需要把J7短接。 |

| SOFT_TCK | GPIOL_N_11 | E3 | |

| SOFT_TDI | GPIOR_N_19 | A10 | |

| SOFT_TDO | GPIOL_P_11 | E2 |

表8

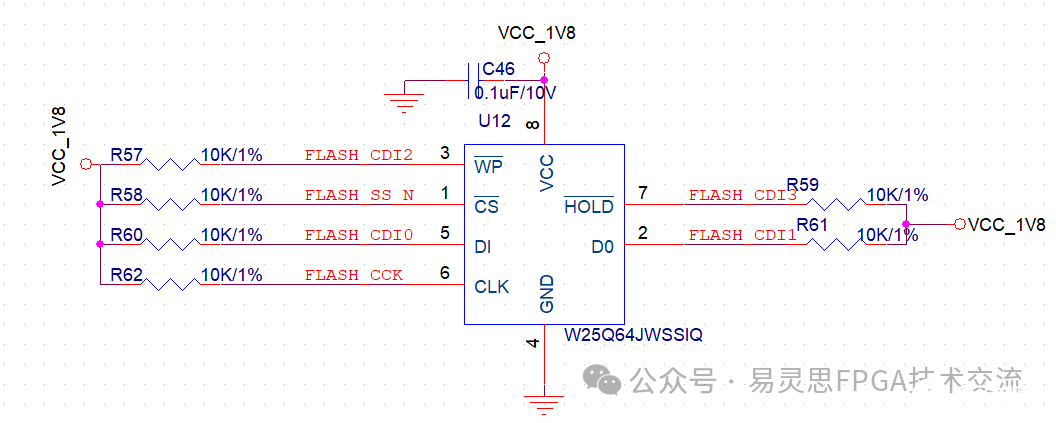

(5)扩展flash

Ti60F100内部自带16Mb的Flash,但是很多客户反馈片上Flash容量偏小,需要扩展。所以底板上提供一个外部GD25LQ64的flash 用于扩展使用,并支持4线。

| 按键编号 | FPGA Name | FPGA Num | 说明 |

| FLASH_CDI0 | GPIOL_P_03 | H2 | 注意,外部扩展flash与合封的flash是共用CCK,CDI0和CDI1. |

| FLASH_CDI1 | GPIOL_P_03 | H1 | |

| FLASH_CDI2 | GPIOL_P_05 | G4 | |

| FLASH_CDI3 | GPIOL_N_05 | G3 | |

| FLASH_SS_N | GPIOT_P_01 | A4 | |

| FLASH_CCK | GPIOL_N_01 | J2 |

表9

(6)HDMI输出

底板J3为HDMI输出,分辨率最高支持1080p60,方便画面显示。

| SIGNAL | FPGA Name | FPGA Num | 说明 |

| TX_TMDS_CLK_P | GPIOR_P_11_CLK8_P | D8 | |

| TX_TMDS_CLK_N | GPIOR_N_11_CLK8_N | D9 | |

| TX_TMDS_DATA_P2 | GPIOR_P_13 | C8 | |

| TX_TMDS_DATA_N2 | GPIOR_N_13 | B8 | |

| TX_TMDS_DATA_P1 | GPIOR_P_14 | B9 | |

| TX_TMDS_DATA_N1 | GPIOR_N_14 | B10 | |

| TX_TMDS_DATA_P0 | GPIOR_P_12 | D10 | |

| TX_TMDS_DATA_N0 | GPIOR_N_12 | C10 |

表9

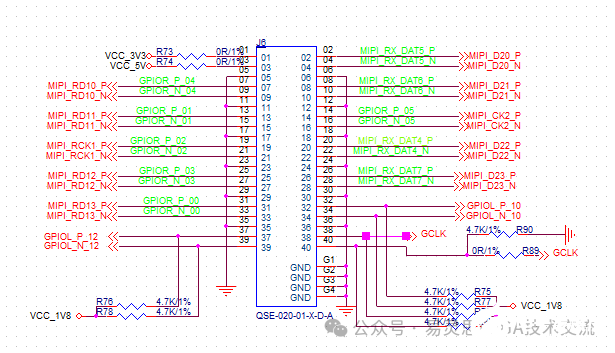

(7)MIPI扩展

在J1座子上预留了10对差分对,可以用于1组4lane的MIPI CSI/DSI接收和1组4lane CSI/DSI发送,也可以用组MIPI CSI/DSI 发送。等长为3mil

当该Bank电压配置为1.8V时,可以用作LVDS,最大10对差分对接收或者发送。

| PIN | PIN | ||

| 1 | 3.3V | 2 | GPIOR_P_08_CLK11_P |

| 3 | 5V | 4 | GPIOR_N_08_CLK11_N |

| 5 | GND | 6 | GND |

| 7 | GPIOR_P_04 | 8 | GPIOR_P_07 |

| 9 | GPIOR_N_04 | 10 | GPIOR_N_07 |

| 11 | GND | 12 | GND |

| 13 | GPIOR_P_01 | 14 | GPIOR_P_05 |

| 15 | GPIOR_N_01 | 16 | GPIOR_N_05 |

| 17 | GND | 18 | GND |

| 19 | GPIOR_P_02 | 20 | GPIOR_P_09_CLK10_P |

| 21 | GPIOR_N_02 | 22 | GPIOR_N_09_CLK10_N |

| 23 | GND | 24 | GND |

| 25 | GPIOR_P_03 | 26 | GPIOR_P_06 |

| 27 | GPIOR_N_03 | 28 | GPIOR_N_06 |

| 29 | GND | 30 | GND |

| 31 | GPIOR_P_00_PLLIN0 | 32 | GPIOL_P_10 |

| 33 | GPIOR_N_00 | 34 | GPIOL_N_10 |

| 35 | GND | 36 | GND |

| 37 | GPIOL_P_12 | 38 | GPIOL_P_09 |

| 39 | GPIOL_N_12 | 40 | GPIOL_P_09 |

表10

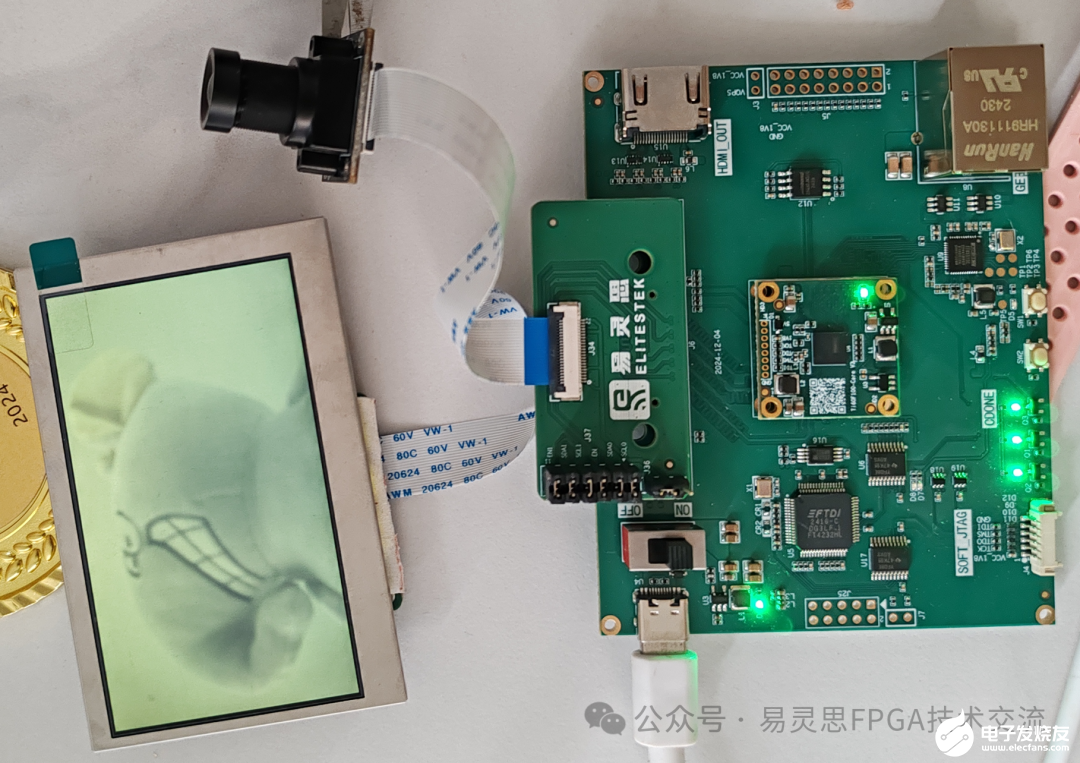

MIPI分配规则,当作为发送时,可支持两组MIPI X4发送;当作为接收时,只有紫色一组可以作为接收,因为只有GPIOR_PN_02可以作为接收时钟。下图是同时接有Senosr和屏的图片。

(8)LVDS扩展

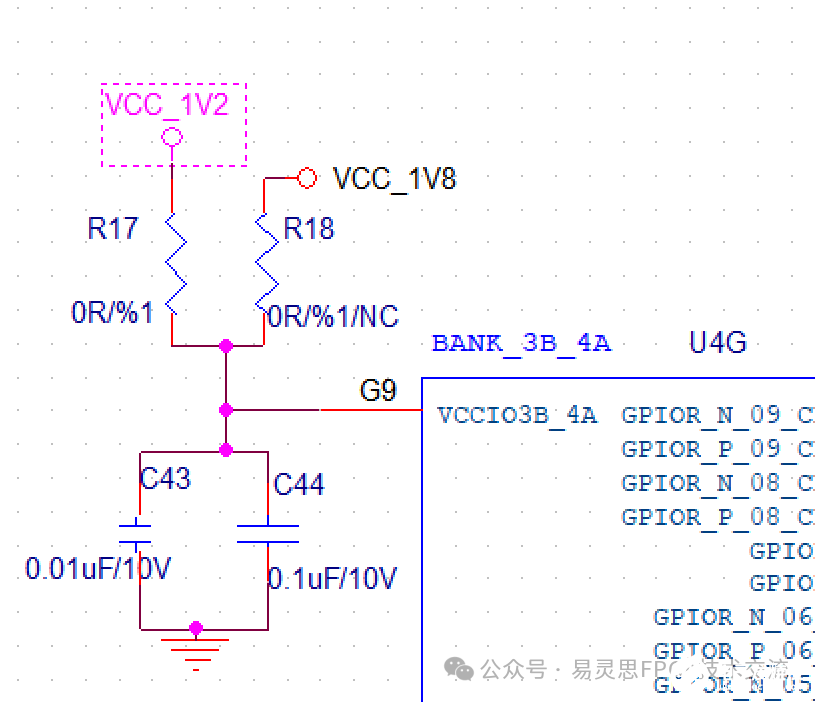

在表10中,10对带颜色的差分做都做了等长,底板3mil,核心板3mil。其中GPIOR_PN_00可以用作LVDS时钟接收连接于PLL。在设计中这些差分对所在的Bank默认Bank电压是1.2V,所以如果要用作LVDS需要把该Bank的电压修改成1.8V,也就是贴上R18,断开R17.

请注意MIPI和LVDS是共用IO的。

(9)GE口

底板提供了三速以太网接口。采用的是裕泰的YT8531SH。

| SIGNAL | FPGA Name | FPGA Num | 说明 |

| TX_CLK | GPIOL_P_06 | G1 | |

| TXD0 | GPIOL_N_06 | F1 | |

| TXD1 | GPIOL_P_15 | C5 | |

| TXD2 | GPIOL_N_15_TEST_N | D5 | |

| TXD3 | GPIOL_N_18 | B2 | |

| TX_CTL | GPIOL_N_09_MIPI_CKN | F2 | |

| RX_CLK | GPIOL_P_08 | E4 | |

| RXD0 | GPIOL_P_17 | B4 | |

| RXD1 | GPIOL_N_07 | F5 | |

| RXD2 | GPIOL_N_08 | E5 | |

| RXD3 | GPIOL_P_18_PLLIN | B3 | |

| RX_CTL | GPIOL_N_17 | C4 | |

| MDIO | GPIOL_P_13 | B1 | |

| MDC | GPIOL_N_13 | C1 |

表11

(10)加密验证

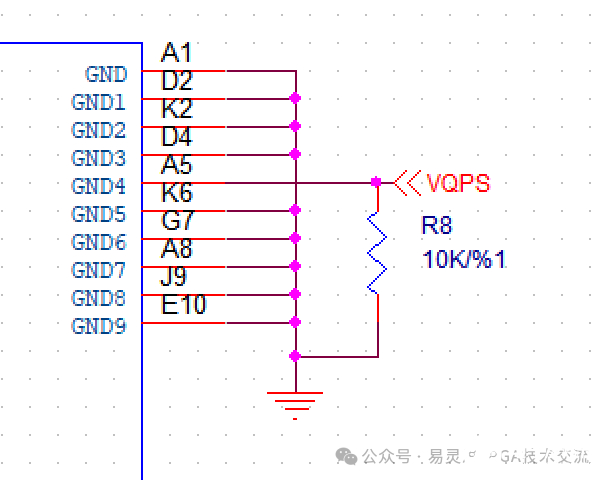

Ti60F100-DK支持加密验证。VQPS默认10K电阻下拉到地。如果需要验证加密功能,短接J3座子给VQPS供电,加密烧写完成之后再断开J3;如果不需要验证直接把J3断开即可。

下一篇:基于FPGA的串口UART设计

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有